AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概...

Transcript of AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概...

![Page 1: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/1.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 1 -

1. 概 要

AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit DAC、

サンプリング周波数192kHzまで対応の4系統ステレオSRC,4系統モノラルSRC, DITに加え,Audio処理

やVoice処理に対応したDSPを内蔵したLSIです。DSP1,DSP2は6144step/fs (48kHzサンプリング時)の

演算能力を持ちます。DSP1とDSP2は異なるサンプリング周波数で動作可能のため、音響処理と同時に、

ハンズフリー(HF)処理をすることも可能です。RAMベースDSPのため、プログラムを書き換えることで、

ユーザの要望に合わせた音響処理や独自開発の高性能HF機能を実現させることができます。64-pin

HTQFPパッケージの採用により省スペースを実現できます。

2. 特 長

Dual DSP部(DSP1,DSP2):(DSP1,DSP2は同じ仕様、遅延用RAMのみ共用)

- データ幅: 37-bit (Data RAM: 浮動小数点対応)

- 動作クロック 294.912MHz (6144steps, fs= 48kHz時)

- 乗算器: 32 x 32 → 64-bit (倍精度演算可)

- 除算器: 32 / 32 → 32-bit (浮動小数正規化機能付き)

- ALU: 96bit算術演算 (with overflow margin 32-bit)

- プログラムRAM (PRAM): 10kword x 36-bit (DSP1), 8kword x 36-bit (DSP2)

- 係数RAM (CRAM): 6kword x 32-bit (DSP1), 6kword x 32-bit (DSP2)

- データRAM (DRAM): 6kword x 37-bit (DSP1), 6kword x 37-bit (DSP2)

- 遅延用RAM(DLRAM): 36kword x 37-bit (DSP1+DSP2 Total)

- JX pins (Interrupt)

- 独立したパワーマネージメント

Sub DSP部(DSP3):

- データ幅: 37-bit (Data RAM: 浮動小数点対応)

- 動作クロック 294.912MHz (6144steps, fs= 48kHz時)

- 乗算器: 32 x 32 → 64-bit (倍精度演算可)

- 除算器: 32 / 32 → 32-bit (浮動小数正規化機能付き)

- ALU: 96bit算術演算 (with overflow margin 32-bit)

- プログラムRAM (PRAM): 2kword x 36-bit

- 係数RAM (CRAM): 4kword x 32-bit

- データRAM (DRAM): 6kword x 37-bit

ADC1: MICゲインアンプ内蔵 24-bit ステレオADC

- サンプリング周波数: fs=8kHz to 48kHz

- チャネル独立アナログゲインアンプ (-3 to 30dB (3dB step))

- 差動、シングルエンド入力、疑似差動入力

- ADC 特性 S/N: 95dB (fs=48kHz, 差動入力, MICゲイン = 0dB)

- チャネル独立ディジタルボリューム (+24 to -103dB, 0.5dB Step, Mute)

- DCオフセットキャンセル用ディジタルHPF

- 低ノイズ MICパワー出力: 2ch

- 選択可能な5種類のディジタルフィルタ

AK7739 4ch CODEC & SRC内蔵Multi Core DSP

![Page 2: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/2.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 2 -

ADC2: 入力セレクタ内蔵 24-bit ステレオADC

- サンプリング周波数: fs=8kHz to 192kHz

- アナログ入力セレクタ: 差動入力 or シングルエンド入力, 疑似差動入力

- ADC特性 S/N: 102dB (fs=48kHz, 差動入力)

- チャネル独立ディジタルボリューム (+24 to -103dB, 0.5dB Step, Mute)

- DCオフセットキャンセル用ディジタルHPF

- 選択可能な5種類のディジタルフィルタ

DAC: Advanced 32-bit DAC

- 2ch x2

- サンプリング周波数: fs=8kHz to 192kHz

- シングルエンド出力

- DAC特性 S/N: 108dB (fs=48kHz)

- チャネル独立ディジタルボリューム (+12 to -115dB, 0.5dB Step, Mute)

- 選択可能な4種類のディジタルフィルタ

SRC部

- 2ch x 4系統 (ステレオ)

- 1ch x 4系統(モノラル) or 2ch x 2系統(ステレオ)

- FSI = 8kHz ~ 192kHz, FSO= 8kHz ~ 192kHz (FSO/FSI= 0.167 ~ 6.0)

DIT部

- S/PDIF,IEC60958,AES/EBU,EIAJ CP1201 民生モード対応

Digital Interfaces

- ディジタル入力ポート6 (Max. @Fs:48kHz TDM使用時 96ch / @Fs:96kHz TDM使用時 48ch)

- ディジタル出力ポート6 (Max. @Fs:48kHz TDM使用時 96ch / @Fs:96kHz TDM使用時 48ch)

- 独立LRCK/BICK入出力ポート x 5系統

- データフォーマット: 前詰32, 24-bit/ 後詰24, 20, 16-bit/ I2S

- Shot/ Long Frame対応

- TDM入出力モード対応 (全入出力ポート対応/512モードx2)

- ディジタルマイク入力ポート (2ch x 1系統)

- SPIインタフェースMaster Controller

ディジタルミキサー回路内蔵 (x2)

PLL回路内蔵

µPインタフェース: SPI (7MHz Max.) / I2C (400KHz Fast Mode)

電源電圧:

Digital: VDD12: 1.14V ~ 1.3V (Typ. 1.2V) I/F: TVDD1: 1.7V ~ 3.6V (Typ. 3.3V)

TVDD2: 1.7V ~ 3.6V (Typ. 3.3V) TVDD3: 1.7V ~ 3.6V (Typ. 3.3V) AVDD: 3.13V ~ 3.6V (Typ. 3.3V)

動作温度範囲: Ta= -40 ~ 85ºC

パッケージ: 64-pin HTQFP (10mm x 10mm, 0.5mm pitch)

![Page 3: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/3.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 3 -

3. 目 次

1. 概 要................................................................................................................................................ 1

2. 特 長................................................................................................................................................ 1

3. 目 次................................................................................................................................................ 3

4. ブロック図 ........................................................................................................................................ 4

■ デバイスブロック図 ............................................................................................................................4

5. ピン配置と機能説明 .......................................................................................................................... 5

■ ピン配置図 ...........................................................................................................................................5

■ 機能説明 ...............................................................................................................................................6

■ 使用しないピンの処理について ........................................................................................................10

■ パワーダウン時のピンの状態一覧 ....................................................................................................11

6. 絶対最大定格 ................................................................................................................................... 12

7. 推奨動作条件 ................................................................................................................................... 13

8. 電気的特性 ...................................................................................................................................... 14

■ アナログ特性 .....................................................................................................................................14 ■ SRC1~4 ..............................................................................................................................................18 ■ SRC5~8 ..............................................................................................................................................19 ■ 消費電流 .............................................................................................................................................20

9. ディジタルフィルタ特性 ................................................................................................................ 21

10. DC特性 ............................................................................................................................................ 31

11. スイッチング特性 ........................................................................................................................... 32

12. 外部接続回路例 ............................................................................................................................... 42

■ 接続図 ................................................................................................................................................42

■ 周辺回路 .............................................................................................................................................43

13. パッケージ ...................................................................................................................................... 45

■ 外形寸法図 .........................................................................................................................................45

■ 材質・メッキ仕様 ..............................................................................................................................45

■ マーキング .........................................................................................................................................46

14. オーダリングガイド ........................................................................................................................ 46

■ オーダーリングガイド .......................................................................................................................46

15. 改定履歴 .......................................................................................................................................... 46

重要な注意事項 ........................................................................................................................................ 47

![Page 4: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/4.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 4 -

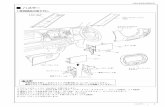

4. ブロック図

■ デバイスブロック図

DAC1

SRC1 (stereo)

CLKGEN &

CONT&

DIT

MPREF

MPWR1

AIN1L/INP1/DMDAT1INN1/DMCLK1

AIN2LN/AIN4LAIN2LP/AIN3L

AIN2RP/AIN3RAIN2RN/AIN4R

LRCK1

BICK1

XTO

PDN

MICBIAS

LRCK2

BICK2

LRCK3

BICK3

LRCK4/CLKO/RDY

BICK4

DSP2

DIN201DIN202DIN203DIN204

DOUT201

GP20

DOUT202DOUT203

DOUT204

GP21

DSP1

DIN101

DIN102

DIN103DIN104

DOUT101

GP10

DOUT102

DOUT103

GP11

ESDI/SDIN5/JX2

SDIN4

SDIN3/JX1

SDIN2/JX0

SDIN1

STO/SDOUT4/RDY

SDOUT3/GPO1/SBST

SDOUT1

SDOUT2/GPO0

AOUT1L

AOUT1R

AOUT2L

AOUT2R

SO/SDA

SELE / SI

SCLK/SCL

CADN/CSN

MLRCLKMBITCLK

MCLK

MDSPCLK

PLLCLK

Sub DSP(DSP3)

SRC2 (stereo)

DAC2

SRC3 (stereo)

SRC4 (stereo)

SRC5 (mono)

Serial IF

AVDDAVSS

TVDD1TVDD2

DV

SS

VD

D1

2

MICIF(I2C)

SRC6 (mono)

ESDO/LRCK5/CLKO

ESCLK/BICK5

ECSO/SDOUT5/GPO2/CLKO

Mixer

DIN205 DOUT205

DIN105 DOUT105

AIN1R/INP2/DMDAT2INN2/DMCLK2

GNDIN4

ADC1

ADC2

SRC7 (mono)

SRC8 (mono)

SDOUT6/DIT/GPO3/CLKO

TVDD3

SDIN6/JX3

DIN106 DOUT106

DIN206 DOUT206

Serial IF

Serial IF

Serial IF

Serial IF

Serial IF

Serial IF

Serial IF

Serial IF

Serial IF

Serial IF

Serial IF

DMIC IF2

DMIC IF1MPWR2

VCOM

XTI

VREFLVREFH

JX21JX20

JX22JX23

JX11JX10

JX12JX13

DOUT104

Figure 1. AK7739全体ブロック図

![Page 5: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/5.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 5 -

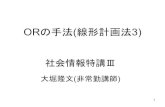

5. ピン配置と機能説明

■ ピン配置図

MP

RE

F

AV

SS

AV

DD

XT

I

XT

O

DV

SS

VD

D12

PD

N

SE

LE

/SI

SC

L/S

CLK

SD

A/S

O

CA

DN

/CS

N

ST

O/S

DO

UT

4/R

DY

SD

IN4

DV

SS

TV

DD

2

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

MPWR1 49 32 BICK4

MPWR2 50 TVDD2 31 LRCK4/CLKO/RDY

INN1/GNDIN1L/DMCLK1 51 30 BICK3

INP1/AIN1L/DMDAT1 52 29 LRCK3

INP2/AIN1R/DMDAT2 53 28 SDIN3/JX1

INN2/GNDIN1R/DMCLK2 54 27 SDOUT3/GPO1/SBST

AIN2LN/AIN4L 55 26 DVSS

AIN2LP/AIN3L 56 25 VDD12

GNDIN4 57 24 SDOUT6/DIT/GPO3/CLKO

AIN2RP/AIN3R 58 23 ESCLK/BICK5

AIN2RN/AIN4R 59 TVDD3 22 ESDO/LRCK5/CLKO

VCOM 60 21 ECSO/SDOUT5/GPO2/CLKO

AVDD 61 AVDD 20 DVSS

AVSS 62 19 TVDD3

VREFH 63 TVDD1 18 ESDI/SDIN5/JX2

VREFL 64 17 SDIN6/JX3

1 2 3 4 5 6 7 8 9 10

11

12

13

14

15

16

AO

UT

1L

AO

UT

1R

AO

UT

2L

AO

UT

2R

VD

D12

DV

SS

SD

IN1

SD

OU

T1

BIC

K1

LR

CK

1

SD

IN2/J

X0

TV

DD

1

DV

SS

S

DO

UT

2/G

PO

0

BIC

K2

LR

CK

2

64pin HTQFP( Top View )

Input

Output

I / O

Power

![Page 6: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/6.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 6 -

■ 機能説明

No. Pin Name I/O Function 供給電源

1 AOUT1L O DAC1 Lch出力ピン AVDD

2 AOUT1R O DAC1 Rch出力ピン AVDD

3 AOUT2L O DAC2 Lch 出力ピン AVDD

4 AOUT2R O DAC2 Rch 出力ピン AVDD

5 VDD12 - ディジタル電源ピン Typ. 1.2V (1.14V ~ 1.3V) -

6 DVSS - ディジタルグランドピン 0V -

7 SDIN1 I シリアルディジタルデータ入力 1ピン TVDD1

8 SDOUT1 O シリアルディジタルデータ出力 1ピン TVDD1

9 BICK1 I/O シリアルビットクロック 1ピン TVDD1

10 LRCK1 I/O LRチャネル選択 1ピン TVDD1

11 SDIN2 I シリアルディジタルデータ入力 2ピン

TVDD1 JX0 I 外部条件ジャンプ入力 0ピン (DSPの JX0入力)

12 TVDD1 - ディジタル IO 電源 1ピン Typ. 3.3V (1.7V ~ 3.6V) -

13 DVSS - ディジタルグランドピン 0V -

14 SDOUT2 O シリアルディジタルデータ出力 2ピン

TVDD1 GPO0 O プログラマブル出力 0ピン (DSP1の GPO0出力)

15 BICK2 I/O シリアルビットクロック 2ピン TVDD1

16 LRCK2 I/O LRチャネル選択 2ピン TVDD1

17 SDIN6 I シリアルディジタルデータ入力 6ピン

TVDD3 JX3 I 外部条件ジャンプ入力 3ピン (DSPの JX3入力)

18

ESDI I 外部デバイスの SPIコントロール用データ入力ピン

(相手側 SO) (プルダウン抵抗付き) TVDD3

SDIN5 I シリアルディジタルデータ入力 5ピン

JX2 I 外部条件ジャンプ入力 2ピン (DSPの JX2入力)

19 TVDD3 - ディジタル IO 電源 3ピン Typ. 3.3V (1.7V ~ 3.6V) -

20 DVSS - ディジタルグランドピン 0V -

![Page 7: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/7.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 7 -

No. Pin Name I/O Function 供給電源

21

ECSO O 外部デバイスの SPIコントロール用出力ピン

(相手側 CS)

TVDD3 SDOUT5 O シリアルディジタルデータ出力 5ピン

GPO2 O プログラマブル出力 2ピン (DSP2の GPO0出力)

CLKO O マスタクロック出力ピン

22

ESDO O 外部デバイスの SPIコントロール用データ出力ピン

(相手側 SI) TVDD3

LRCK5 I/O LRチャネル選択 5ピン

CLKO O マスタクロック出力ピン

23 ESCLK O

外部デバイスの SPIコントロール用クロック出力ピン

(相手側 SCLK) TVDD3

BICK5 I/O シリアルビットクロック 5ピン

24

SDOUT6 O シリアルディジタルデータ出力 6ピン

TVDD3 DIT O DIT出力ピン

GPO3 O プログラマブル出力 3ピン (DSP2の GPO3出力)

CLKO O マスタクロック出力ピン

25 VDD12 - ディジタル電源ピン Typ. 1.2V (1.14V ~ 1.3V) -

26 DVSS - ディジタルグランドピン 0V -

27

SDOUT3 O シリアルディジタルデータ出力 3ピン

TVDD2 GPO1 O プログラマブル出力 1ピン (DSP1の GPO1出力)

SBST O セルフブートステータス (SELE pin =”H”時有効)

28 SDIN3 I シリアルディジタルデータ入力 3ピン

TVDD2 JX1 I 外部条件ジャンプ入力 1ピン (DSPの JX1入力)

29 LRCK3 I/O LRチャネル選択 3ピン TVDD2

30 BICK3 I/O シリアルビットクロック 3ピン TVDD2

31

LRCK4 I/O LRチャネル選択 4ピン

TVDD2 CLKO O マスタクロック出力ピン

RDY O RDY信号出力ピン

32 BICK4 I/O シリアルビットクロック 4ピン TVDD2

33 TVDD2 - ディジタル IO 電源 2ピン Typ. 3.3V (1.7V ~ 3.6V) -

34 DVSS - ディジタルグランドピン 0V -

35 SDIN4 I シリアルディジタルデータ入力 4ピン TVDD2

![Page 8: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/8.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 8 -

No. Pin Name I/O Function 供給電源

36

STO O ステータス信号出力ピン

・パワーダウン時の出力は“H”です。 TVDD2

SDOUT4 O シリアルディジタルデータ出力 4ピン

RDY O RDY信号出力ピン

37

CADN I

I2Cモード:I2Cインタフェース用バスアドレス Nピン

・プルアップ、またはプルダウンで使用してください。

極性を反転したものをバスアドレスとして使用します。 TVDD2

CSN I

SPIモード:SPIインタフェース用チップセレクト Nピン

・パワーダウン状態、またはマイコンとのインタフェースを行わな

い場合は “H”にして下さい。

38 SDA I/O I2Cインタフェース SDAピン

TVDD2 SO O SPIインタフェース用シリアルデータ出力ピン

39 SCL I I2Cインタフェース用シリアルデータクロック入力ピン

TVDD2 SCLK I SPIインタフェース用シリアルデータクロック入力ピン

40 SELE I セルフブートイネーブルピン (CSN pin= “H”の時有効)

TVDD2 SI I SPIインタフェース用シリアルデータ入力ピン

41 PDN I

パワーダウン Nピン

・本製品をパワーダウンする際に使用します。

“L”: Power Down, “H”: Normal Operation

・電源立ち上げ時は”L”にしてください。

TVDD2

42 VDD12 - ディジタル電源ピン Typ. 1.2V (1.14V ~ 1.3V) -

43 DVSS - ディジタルグランドピン 0V -

44 XTO O

発振回路出力ピン

・水晶振動子を使用する場合、水晶振動子を XTI Pin と XTO Pinに

接続してください。

・水晶振動子を使用しない場合は、オープンにしてください。

AVDD

45 XTI I

発振回路入力ピン

・水晶振動子を使用する場合、水晶振動子を XTI Pin と XTO Pinに

接続してください。

・水晶振動子を使用しない場合は、外部クロックに接続又は AVSS

に接続してください。

AVDD

46 AVDD - アナログ電源ピン Typ. 3.3V (3.13V ~ 3.6V) -

47 AVSS - アナロググランドピン 0V -

![Page 9: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/9.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 9 -

No. Pin Name I/O Function 供給電源

48 MPREF O

マイクパワー電源 リップルフィルタピン

・1µFのセラミックコンデンサを AVSSとの間に接続してくださ

い。

・外部回路には使用しないで下さい。

AVDD

49 MPWR1 O マイク用電源出力 1ピン (パワーダウン時の出力は“Hi-Z”) AVDD

50 MPWR2 O マイク用電源出力 2ピン (パワーダウン時の出力は“Hi-Z”) AVDD

51

INN1 I ADC1 Lch 差動反転入力 1ピン

AVDD GNDIN1L I ADC1 Lch 疑似差動グランド入力 1ピン

DMCLK1 O ディジタルマイククロック出力 1ピン

52

INP1 I ADC1 Lch 差動非反転入力 1ピン

AVDD AIN1L I ADC1 Lch シングルエンド/疑似差動入力 1ピン

DMDAT1 I ディジタルマイクデータ入力 1ピン

53

INP2 I ADC1 Rch 差動非反転入力 2ピン

AVDD AIN1R I ADC1 Rch シングルエンド/疑似差動入力 1ピン

DMDAT2 I ディジタルマイクデータ入力 2ピン

54

INN2 I ADC1 Rch 差動反転入力 2ピン

AVDD GNDIN1R I ADC1 Rch 疑似差動グランド入力 1ピン

DMCLK2 O ディジタルマイククロック出力 2ピン

55 AIN2LN I ADC2 Lch 差動反転入力 2ピン

AVDD AIN4L I ADC2 Lch シングルエンド入力 4ピン

56 AIN2LP I ADC2 Lch 差動非反転入力 2ピン

AVDD AIN3L I ADC2 Lch シングルエンド入力 3ピン

57 GNDIN4 I ADC2 疑似差動グランド入力 4ピン AVDD

58 AIN2RP I ADC2 Rch 差動非反転入力 2ピン

AVDD AIN3R I ADC2 Rch シングルエンド入力 3ピン

59 AIN2RN I ADC2 Rch 差動反転入力 2ピン

AVDD AIN4R I ADC2 Rch シングルエンド入力 4ピン

60 VCOM O

アナログ部コモン電圧出力ピン

・2.2µFのセラミックコンデンサを AVSSとの間に接続してくだ

さい。

・外部回路には使用しないで下さい。

AVDD

61 AVDD - アナログ電源ピン 3.3V (typ) -

62 AVSS - アナロググランドピン 0V -

63 VREFH - CODECアナログハイレベルリファレンスピン (AVDD と接続) AVDD

64 VREFL - CODECアナログローレベルリファレンスピン (AVSSと接続) AVDD

- 裏面 TAB - ボードのグランドに接続してください。 -

![Page 10: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/10.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 10 -

■ 使用しないピンの処理について

Table 1. 使用しない入出力ピンの処理

Classification Pin Name Setting

Analog

AOUT1L, AOUT1R, AOUT2L, AOUT2R,XTO, MPREF, MPWR1, MPWR2,INN1/GNDIN1L/DMCLK1, INP1/ AIN1L/DMDAT1, INP2/ AIN1R/DMDAT2,INN2/GNDIN1R/DMCLK2, AIN2LN/AIN4L, AIN2LP/AIN3L, GNDIN4,AIN2RP/AIN3R, AIN2RN/AIN4R, VCOM

オープン

XTI AVSSに接続

Digital

SDOUT1, SDOUT2/GPO0, ECSO/SDOUT5/GPO2/CLKO, ESDO/LRCK5/CLKO, ESCLK/BICK5, SDOUT6/DIT/GPO3/CLKO, SDOUT3/GPO1/SBST, STO/SDOUT4/RDY, SDA/SO

オープン

SDIN1, BICK1, LRCK1, SDIN2/JX0, BICK2, LRCK2, SDIN6/JX3, ESDI/SDIN5/JX2, SDIN3/JX1,LRCK3,BICK3, LRCK4/CLKO/RDY, BICK4, SDIN4, CADN/CSN, SCL/SCLK, SELE/SI

DVSSに接続

使用しない入出力ピンはTable 1の設定を行い、適切に処理してください。

![Page 11: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/11.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 11 -

■ パワーダウン時のピンの状態一覧

No Pin Name パワーダウン状態

PDN pin = ”L” No Pin Name

パワーダウン状態

PDN pin = ”L”

1 AOUT1L “Hi-Z” 32 BICK4 Input (プルダウン typ.51kΩ)

2 AOUT1R “Hi-Z” 33 TVDD2 -

3 AOUT2L “Hi-Z” 34 DVSS -

4 AOUT2R “Hi-Z” 35 SDIN4 Input (Hi-Z)

5 VDD12 - 36 STO “H”

6 DVSS - SDOUT4

7 SDIN1 Input (Hi-Z) RDY

8 SDOUT1 “L” 37 CADN Input (Hi-Z)

9 BICK1 Input (プルダウン typ.51 kΩ) CSN

10 LRCK1 Input (プルダウン typ.51 kΩ) 38 SDA “Hi-Z”

11 SDIN2

Input (Hi-Z) 39

SO

JX0 SCL Input (Hi-Z)

12 TVDD1 - SCLK

13 DVSS - 40 SELE Input (Hi-Z)

14 SDOUT2

“L” SI

GPO0 41 PDN Input (“L”フォース)

15 BICK2 Input (プルダウン typ.51 kΩ) 42 VDD12 -

16 LRCK2 Input (プルダウン typ.51 kΩ) 43 DVSS -

17 SDIN6

Input (Hi-Z) 44 XTO “H”

JX3 45 XTI “H”(プルアップ typ.1103kΩ)

18

ESDI

Input (Hi-Z)

46 AVDD -

47 AVSS -

SDIN5 48 MPREF “L”(プルダウン typ.111 kΩ)

JX2 49 MPWR1 “Hi-Z”

19 TVDD3 - 50 MPWR2 “Hi-Z”

20 DVSS -

51

INN1

“Hi-Z”

21

ECSO

“H”

GNDIN1L

SDOUT5 DMCLK1

GPO2

52

INP1

“Hi-Z” CLKO AIN1L

22

ESDO

“L”

DMDAT1

LRCK5

53

INP2

“Hi-Z” CLKO AIN1R

23 ESCLK

“L” DMDAT2

BICK5

54

INN2

“Hi-Z”

24

SDOUT6

“L”

GNDIN1R

DIT DMCLK2

GPO3 55

AIN2LN “Hi-Z”

CLKO AIN4L

25 VDD12 - 56

AIN2LP “Hi-Z”

26 DVSS - AIN3L

27

SDOUT3

“L”

57 GNDIN4 “Hi-Z”

GPO1 58

AIN2RP “Hi-Z”

SBST AIN3R

28 SDIN3

Input (Hi-Z) 59 AIN2RN

“Hi-Z” JX1 AIN4R

29 LRCK3 Input (プルダウン typ.51 kΩ) 60 VCOM “L”(プルダウン typ.300Ω)

30 BICK3 Input (プルダウン typ.51 kΩ) 61 AVDD -

31

LRCK4 Input (プルダウン typ.51 kΩ) 62 AVSS -

CLKO 63 VREFH “Hi-Z”

RDY 64 VREFL “Hi-Z”

![Page 12: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/12.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 12 -

6. 絶対最大定格

(AVSS = DVSS = 0V; * 1)

Parameter Symbol Min. Max. Unit

電源電圧

Analog Digital1(Core) Digital2(I/F)

Digital3(I/F) Digital4(I/F) Difference (AVSS,DVSS) (* 1)

AVDD VDD12 TVDD1 TVDD2 TVDD3 ΔGND

-0.3 -0.3 -0.3 -0.3 -0.3 -0.3

3.9 1.4 3.9 3.9 3.9 0.3

V V V V V

アナログ入力電圧 (* 2) VINA -0.3 (AVDD+0.3) or 3.9 V

ディジタル入力電圧 (* 3) VIND1 -0.3 (TVDD1+0.3) or 3.9 V

ディジタル入力電圧 (* 4) VIND2 -0.3 (TVDD2+0.3) or 3.9 V

ディジタル入力電圧 (* 5) VIND3 -0.3 (TVDD3+0.3) or 3.9 V

動作周囲温度 Ta -40 85 ºC

保存温度 Tstg -65 150 ºC

Notes:

* 1. すべての電圧はグラウンドに対する値です。AVSSとDVSSは同電位にして下さい。

* 2. アナログ入力電圧のMax.値は,(AVDD+0.3)Vまたは3.9Vのどちらか低い方です。

* 3. 供給電源がTVDD1の入力・入出力ピンのディジタル入力電圧のMax.値は、(TVDD1+0.3)Vまたは

3.9Vのどちらか低い方です。

* 4. 供給電源がTVDD2の入力・入出力ピンのディジタル入力電圧のMax.値は、(TVDD2+0.3)Vまたは

3.9Vのどちらか低い方です。

* 5. 供給電源がTVDD3の入力・入出力ピンのディジタル入力電圧のMax.値は、(TVDD3+0.3)Vまたは

3.9Vのどちらか低い方です。

注意: この値を超えた条件で使用した場合、デバイスを破壊することがあります。また通常の動作は保

証されません。

![Page 13: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/13.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 13 -

7. 推奨動作条件

(AVSS = DVSS = 0V; * 1)

Parameter Symbol Min. Typ. Max. Unit

電源電圧

Analog Digital (1.2V Core)

Digital (I/F)

AVDD VDD12

TVDD1,2,3

3.13 1.14 1.7

3.3 1.2 3.3

3.6 1.3 3.6

V V V

Notes:

* 6. VDD12を立ち上げる際は、AVDD,TVDD1-3と同時または後に立ち上げて下さい。VDD12を立ち下

げる際は、AVDD,TVDD1-3と同時または先に立ち下げて下さい。PDN pin = “L”の状態で各電源を立

ち上げ、全ての電源が立ち上がった後、PDN pin = “H”にしてください。

* 7. I2Cインタフェースを使用する場合、周辺デバイスが電源ONの状態で本製品の電源をOFFにしない

で下さい。また、SDA, SCL pinのプルアップ抵抗の接続先はTVDD2以下にして下さい。

注意: 本データシートに記載されている条件以外のご使用に関しては、当社では責任負いかねますので

ご注意下さい。

![Page 14: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/14.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 14 -

8. 電気的特性

■ アナログ特性

1. MIC AMPゲイン

(Ta=25C; AVDD=VREFH=TVDD1=TVDD2=TVDD3= 3.3V, VDD12=1.2V; AVSS=VREFL=DVSS=0V)

MIC AMP

Parameter Min. Typ. Max. Unit

入力インピーダンス 17 25 33 kΩ

Gain

MGNL[3:0]bits=0x0, MGNR[3:0]bits=0x0 -4 -3 -2

dB

MGNL[3:0]bits=0x1, MGNR[3:0]bits=0x1 -1 0 1

MGNL[3:0]bits=0x2, MGNR[3:0]bits=0x2 2 3 4

MGNL[3:0]bits=0x3, MGNR[3:0]bits=0x3 5 6 7

MGNL[3:0]bits=0x4, MGNR[3:0]bits=0x4 8 9 10

MGNL[3:0]bits=0x5, MGNR[3:0]bits=0x5 11 12 13

MGNL[3:0]bits=0x6, MGNR[3:0]bits=0x6 14 15 16

MGNL[3:0]bits=0x7, MGNR[3:0]bits=0x7 17 18 19

MGNL[3:0]bits=0x8, MGNR[3:0]bits=0x8 20 21 22

MGNL[3:0]bits=0x9, MGNR[3:0]bits=0x9 23 24 25

MGNL[3:0]bits=0xA, MGNR[3:0]bits=0xA 26 27 28

MGNL[3:0]bits=0xB, MGNR[3:0]bits=0xB 29 30 31

2. マイクバイアス出力

(Ta=25C; AVDD =VREFH=TVDD1=TVDD2=TVDD3= 3.3V, VDD12=1.2V; AVSS =VREFL=DVSS=0V)

MIC Bias

Parameter Min. Typ. Max. Unit

Output Voltage * 8 2.3 2.5 2.7 V

Load Resistance 2 kΩ

Load Capacitance

30 pF

Output Noise (A-weighted) -114 -108 dBV

Notes

* 8. 出力電圧はAVDDに比例(0.76×AVDD)します。

![Page 15: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/15.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 15 -

3. MIC AMP + ADC1

(Ta=25C; AVDD=VREFH=TVDD1=TVDD2=TVDD3= 3.3V, VDD12=1.2V; AVSS=VREFL=DVSS=0V;

信号周波数=1kHz; 24bit Data; BICK=64fs; 測定周波数 BW=20Hz ~ 20kHz @fs=48kHz); MGNL/R[3:0]

bits = 0x1 (0dB)

Notes

* 9. MGNL/R[3:0] bits = 0x1 (0dB)、入力フルスケール電圧はAVDDに比例(0.86×AVDD)します。

* 10. MGNL/R[3:0] bits = 0x7 (+18dB)、入力フルスケール電圧はAVDDに比例(0.108×AVDD)します。

* 11. -1dBFSの信号を入力した場合の、Lch-Rch間のアイソレーションです。

* 12. 差動入力の両方に1kHz, 100mVppの正弦波を重畳した場合の同相信号除去比。差動入力に

1kHz,±100mVppの正弦波を入れた場合を基準とする。

* 13. AVDDおよびVREFHに1kHz, 50mVppの正弦波を重畳した場合。

* 14. 疑似差動入力時。疑似差動入力および疑似差動グランド入力に1kHz, 100mVppの正弦波を

重畳した場合の同相信号除去比。疑似差動入力に 100mVppの正弦波を入れた場合を基準とする。

MIC AMP + ADC1

Parameter Min. Typ. Max. Unit

Resolution 24 bit

Differential Input

Full-scale Input Voltage

* 9 ±2.55 ±2.83 ±3.11 Vpp

* 10 ±0.324 ±0.357 ±0.388

S/(N+D) (-1dBFS)

fs=48kHz * 9 75 85 dB

fs=48kHz * 10 75

Dynamic Range (-60dBFS)

fs=48kHz (A-weighted) * 9 87 95 dB

fs=48kHz (A-weighted)* 10 85

S/N fs=48kHz (A-weighted) * 9 87 95

dB fs=48kHz (A-weighted) * 10 85

Inter-Channel Isolation * 11 90 105 dB

Channel Gain Mismatch 0.0 0.3 dB

PSRR * 13 50 dB

CMRR * 12 60 75 dB

Single-ended Input, Pseudo-differential Input

Full-scale Input Voltage

* 9 2.55 2.83 3.11 Vpp

* 10 0.324 0.357 0.388

S/(N+D) (-1dBFS)

fs=48kHz * 11 72 82 dB

fs=48kHz * 10 72

Dynamic Range (-60dBFS)

fs=48kHz (A-weighted) * 9 84 92 dB

fs=48kHz (A-weighted) * 10 82

S/N fs=48kHz (A-weighted) * 9 84 92

dB fs=48kHz (A-weighted) * 10 82

Inter-Channel Isolation * 11 90 105 dB

Channel Gain Mismatch 0.0 0.3 dB

PSRR * 13 50 dB

CMRR (Pseudo-differential) * 14 70 dB

![Page 16: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/16.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 16 -

4. ADC2

(Ta=25C; AVDD=VREFH=TVDD1=TVDD2=TVDD3=3.3V, VDD12=1.2V; AVSS =VREFL=DVSS=0V;

信号周波数=1kHz; 24bit Data; BICK=64fs; 測定周波数BW=20Hz - 20kHz @fs=48kHz; 測定周波数

BW=20Hz-40kHz @fs=96kHz,192kHz)

Notes

* 15. 対象となる入力ピンはAIN2LP, AIN2LN, AIN2RP, AIN2RNです。入力フルスケール電圧はAVDDに

比例(0.86×AVDD)します。

* 16. 対象となる入力ピンはAIN3L, AIN3R, AIN4L, AIN4Rです。入力フルスケール電圧はAVDDに比例

(0.86×AVDD)します。

ADC2

Parameter Min. Typ. Max. Unit

Resolution 24 bit

Input Impedance 17 25 33 kΩ

Differential Input

Full-scale Input Voltage * 15 ±2.55 ±2.83 ±3.11 Vpp

S/(N+D) (-1dBFS)

fs=48kHz 80 90

dB fs=96kHz 87

fs=192kHz 87

Dynamic Range (-60dBFS)

fs=48kHz (A-weighted) 94 102

dB fs=96kHz 95

fs=192kHz 95

S/N

fs=48kHz (A-weighted) 94 102

dB fs=96kHz 95

fs=192kHz 95

Inter-Channel Isolation * 11 90 105 dB

Channel Gain Mismatch 0.0 0.3 dB

PSRR * 13 50 dB

CMRR * 12 60 80 dB

Single-ended Input, Pseudo-differential Input

Full-scale Input Voltage * 16 2.55 2.83 3.11 Vpp

S/(N+D) (-1dBFS)

fs=48kHz 80 90

dB fs=96kHz 87

fs=192kHz 87

Dynamic Range (-60dBFS)

fs=48kHz (A-weighted) 91 99

dB fs=96kHz 92

fs=192kHz 92

S/N

fs=48kHz (A-weighted) 91 99

dB fs=96kHz 92

fs=192kHz 92

Inter-Channel Isolation * 11 90 105 dB

Channel Gain Mismatch 0.0 0.3 dB

PSRR * 13 50 dB

CMRR (Pseudo-differential) * 14 55 75 dB

![Page 17: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/17.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 17 -

5. DAC

(Ta=25C; AVDD=VREFH=TVDD1=TVDD2=TVDD3= 3.3V, VDD12=1.2V; AVSS =VREFL=DVSS=0V; 信号周波数=1kHz; 32bit Data; BICK=64fs; 測定周波数 BW=20Hz - 20kHz @fs=48kHz; 測定周波数

BW=20Hz - 40kHz @fs=96kHz,192kHz)

DAC1 DAC2

Parameter Min. Typ. Max. Unit

Resolution 32 bit

Output Voltage * 17 2.55 2.83 3.11 Vpp

S/(N+D) (0dBFS)

fs=48kHz 85 95

dB fs=96kHz 92

fs=192kHz 92

Dynamic Range (-60dBFS)

fs=48kHz (A-weighted) 100 108

dB fs=96kHz 101

fs=192kHz 101

S/N

fs=48kHz (A-weighted) 100 108

dB fs=96kHz 101

fs=192kHz 101

Inter-Channel Isolation (fin=1kHz) * 18 90 110 dB

Channel Gain Mismatch 0.0 0.7 dB

Load Resistance * 19 10 kΩ

Load Capacitance 30 pF

PSRR * 13 50 dB

Notes

* 17. フルスケール出力電圧です。出力電圧はAVDDに比例 (AVDD x 0.86)します。

* 18. 0dBFSの信号を入力した場合のAOUT1L, AOUT1R間、AOUT2L, AOUT2R間、AOUT3L, AOUT3R

間のアイソレーションです。

* 19. AC負荷に対して。

![Page 18: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/18.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 18 -

■ SRC1~4

(Ta=25C; AVDD=TVDD1=TVDD2=TVDD3= 3.3V, VDD12=1.2V; AVSS=DVSS=0V; 信号周波数=

1kHz; 32-bit Data; 測定周波数BW=20Hz ~ FSO/2)

SRC

Parameter Symbol Min. Typ. Max. Unit

Resolution 32 bit

Input Sample Rate FSI 8 192 kHz

Output Sample Rate FSO 8 192 kHz

THD+N (Input=1kHz, 0dBFS)

Audioモード(SRCFAUDx=1, SRCFECx=0)

FSO/FSI=192kHz/48kHz FSO/FSI=44.1kHz/48kHz FSO/FSI=48kHz/88.2kHz FSO/FSI=48kHz/96kHz FSO/FSI=44.1kHz/96kHz FSO/FSI=48kHz/192kHz FSO/FSI=8kHz/48kHz

Voiceモード(SRCFAUDx=0, SRCFECx=0)

FSO/FSI=24kHz/32kHz FSO/FSI=16kHz/24kHz FSO/FSI=24kHz/44.1kHz FSO/FSI=16kHz/44.1kHz FSO/FSI=8kHz/32kHz

-132 -131

-131 -185 -123 -185 -185

-97 -100 -80 -71 -177

dB dB dB dB dB dB dB

dB dB dB dB dB

Dynamic Range (Input=1kHz, -60dBFS)

Audioモード(SRCFAUDx=1, SRCFECx=0)

FSO/FSI=192kHz/48kHz FSO/FSI=44.1kHz/48kHz FSO/FSI=48kHz/88.2kHz FSO/FSI=48kHz/96kHz FSO/FSI=44.1kHz/96kHz FSO/FSI=48kHz/192kHz FSO/FSI=8kHz/48kHz

Voiceモード(SRCFAUDx=0, SRCFECx=0)

FSO/FSI=24kHz/32kHz FSO/FSI=16kHz/24kHz FSO/FSI=24kHz/44.1kHz FSO/FSI=16kHz/44.1kHz FSO/FSI=8kHz/32kHz

180 184 183 185 182 185 185

157 160 140 131

179

dB dB dB dB dB dB dB

dB dB dB dB dB

Dynamic Range (Input=1kHz, -60dBFS, A-weighted)

FSO/FSI=44.1kHz/48kHz

186

dB

Ratio between Input and Output Sample Rate FSO/FSI 0.167 6 -

![Page 19: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/19.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 19 -

■ SRC5~8

(Ta=25C; AVDD=TVDD1=TVDD2=TVDD3= 3.3V, VDD12=1.2V; AVSS=DVSS=0V; 信号周波数=1kHz;

24-bit Data; 測定周波数BW=20Hz ~ FSO/2)

SRC

Parameter Symbol Min. Typ. Max. Unit

Resolution 24 bit

Input Sample Rate FSI 8 192 kHz

Output Sample Rate FSO 8 192 kHz

THD+N (Input=1kHz, 0dBFS) Voice Mode (SRCFAUDx=0, SRCFECx=0)

FSO/FSI= 16kHz/ 8kHz FSO/FSI= 44.1kHz/ 48kHz FSO/FSI= 24kHz/ 32kHz FSO/FSI= 16kHz/ 24kHz FSO/FSI= 24kHz/44.1kHz FSO/FSI= 16kHz/44.1kHz FSO/FSI= 8kHz/ 32kHz FSO/FSI= 8kHz/ 48kHz

Audio Mode (SRCFAUDx=1, SRCFECx=0) FSO/FSI= 24kHz/44.1kHz FSO/FSI= 24kHz/ 48kHz FSO/FSI= 16kHz/44.1kHz

- - - - - - - - - - -

-125 -125 -95 -98 -78 -69

-130 -130

-120 -133 -98

- - - - - - - - - - -

dB dB dB dB dB dB dB dB

dB dB dB

Dynamic Range (Input=1kHz, -60dBFS) Voice Mode (SRCFAUDx=0, SRCFECx=0)

FSO/FSI= 16kHz/ 8kHz FSO/FSI= 44.1kHz/ 48kHz FSO/FSI= 24kHz/ 32kHz FSO/FSI= 16kHz/ 24kHz FSO/FSI= 24kHz/44.1kHz FSO/FSI= 16kHz/44.1kHz FSO/FSI= 8kHz/ 32kHz FSO/FSI= 8kHz/ 48kHz

Audio Mode (SRCFAUDx=1, SRCFECx=0) FSO/FSI= 24kHz/44.1kHz FSO/FSI= 24kHz/ 48kHz FSO/FSI= 16kHz/44.1kHz

- - - - - - - - - - -

135 136 134 117 132 128 130 130

136 135 135

- - - - - - - - - - -

dB dB dB dB dB dB dB dB

dB dB dB

Dynamic Range (Input=1kHz, -60dBFS, A-weighted)

FSO/FSI=44.1kHz/48kHz

-

137

-

dB

Ratio between Input and Output Sampling Rate FSO/FSI 0.167 6 -

![Page 20: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/20.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 20 -

■ 消費電流

(Ta= 25ºC; AVDD=3.13~3.6V (Typ.=3.3V, Max.=3.6V); VDD12=1.14 ~ 1.3V (Typ.=1.2V, Max.=1.3V); TVDD1=TVDD2=TVDD3=1.7 ~ 3.6V(Typ.=3.3V, Max.=3.6V); (AVSS,DVSS= 0V)

Parameter Symbol Min. Typ. Max Unit

動作時消費電流 (* 20)

(PDN pin= “H”)

AVDD 30 45 mA

VDD12 160 500 mA

TVDD1 5 8 mA

TVDD2 5 8 mA

TVDD3 5 8 mA

パワーダウン時消費電流

(PDN pin= “L”)

AVDD 0.01 mA

VDD12 1.5 mA

TVDD1 0.01 mA

TVDD2 0.01 mA

TVDD3 0.01 mA

Note:

* 20. VDD12の消費電流値は使用周波数およびDSPプログラム内容によって変化します。

![Page 21: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/21.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 21 -

9. ディジタルフィルタ特性

1. ADC 1~2部

(Ta=-40~85°C; AVDD=3.13~3.6V, TVDD1=TVDD2=TVDD3=1.7~3.6V, VDD12=1.14~1.3V; AVSS =DVSS=0V) 1-1. Sharp Roll-Off Filter (ADxVO bit = “0”(x=1,2), ADSD bit = “0”, ADSL bit = “0” ) fs=48kHz

Parameter Symbol Min. Typ. Max. Unit

SHARP ROLL-OFF

Passband * 21 0dB/-0.06dB PB 0 - 22.1 kHz

-3.0dB PB - 23.7 - kHz

Stopband * 21 SB 27.8 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-20kHz GD - 0 - 1/fs

Group Delay * 22 GD - 20 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 0.9 - Hz

fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

SHARP ROLL-OFF

Passband * 21 0dB/-0.06dB PB 0 - 44.2 kHz

-3.0dB PB - 47.5 - kHz

Stopband * 21 SB 55.6 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-40kHz GD - 0 - 1/fs

Group Delay * 22 GD - 20 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 1.9 - Hz

fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

SHARP ROLL-OFF

Passband * 21 0dB/-0.04dB PB 0 - 83.7 kHz

-3.0dB PB - 96.0 - kHz

Stopband * 21 SB 122.9 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-40kHz GD - 0 - 1/fs

Group Delay * 22 GD - 16 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 3.8 - Hz

* 21. 各振幅特性の周波数はfs(サンプリングレート)に比例します。HPFの特性は含まれていません。

* 22. ディジタルフィルタによる遅延演算で、ADC部はアナログ信号が入力されてから両チャネル

24bitデータが出力レジスタにセットされるまでの時間です。HPFによる群遅延も含みます。

![Page 22: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/22.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 22 -

1-2. Slow Roll-Off Filter (ADxVO bit = “0”(x=1,2), ADSD bit = “0”, ADSL bit = “1” ) fs=48kHz

Parameter Symbol Min. Typ. Max. Unit

SLOW ROLL-OFF

Passband * 21 0dB/-0.074dB PB 0 - 12.5 kHz

-3.0dB - 19.2 - kHz

Stopband * 21 SB 36.5 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-20kHz GD - 0 - 1/fs

Group Delay * 22 GD - 8 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 0.9 - Hz

fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

SLOW ROLL-OFF

Passband * 21 0dB/-0.074dB PB 0 - 25 kHz

-3.0dB - 38.5 - kHz

Stopband * 21 SB 73 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-40kHz GD - 0 - 1/fs

Group Delay * 22 GD - 8 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 1.9 - Hz

fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

SLOW ROLL-OFF

Passband * 21 0dB/-0.1dB PB 0 - 31.1 kHz

-3.0dB - 62.3 - kHz

Stopband * 21 SB 145.9 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-40kHz GD - 0 - 1/fs

Group Delay * 22 GD - 9 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 3.8 - Hz

![Page 23: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/23.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 23 -

1-3. Short Delay Sharp Roll-Off Filter (ADxVO bit = “0”(x=1,2), ADSD bit = “1”, ADSL bit = “0” ) fs=48kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SHARP ROLL-OFF

Passband * 21 0dB/-0.06dB PB 0 - 22.1 kHz

-3.0dB - 23.7 - kHz

Stopband * 21 SB 27.8 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-20kHz GD - - 2.6 1/fs

Group Delay * 22 GD - 6 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 0.9 - Hz

fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SHARP ROLL-OFF

Passband * 21 0dB/-0.06dB PB 0 - 44.2 kHz

-3.0dB - 47.5 - kHz

Stopband * 21 SB 55.6 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-40kHz GD - - 2.6 1/fs

Group Delay * 22 GD - 6 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 1.9 - Hz

fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SHARP ROLL-OFF

Passband * 21 0dB/-0.04dB PB 0 - 83.7 kHz

-3.0dB - 96.0 - kHz

Stopband * 21 SB 122.9 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-40kHz GD - 0 0.2 1/fs

Group Delay * 22 GD - 7 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 3.8 - Hz

![Page 24: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/24.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 24 -

1-4. Short Delay Slow Roll-Off Filter (ADxVO bit = “0”(x=1,2), ADSD bit = “1”, ADSL bit = “1” ) fs=48kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SLOW ROLL-OFF

Passband * 21 0dB/-0.074dB PB 0 - 12.5 kHz

-3.0dB - 19.2 - kHz

Stopband * 21 SB 36.5 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-20kHz GD - - 2.6 1/fs

Group Delay * 22 GD - 6 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 0.9 - Hz

fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SLOW ROLL-OFF

Passband * 21 0dB/-0.074dB PB 0 - 25 kHz

-3.0dB - 38.5 - kHz

Stopband * 21 SB 73 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-40kHz GD - - 2.6 1/fs

Group Delay * 22 GD - 6 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 1.9 - Hz

fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SLOW ROLL-OFF

Passband * 21 0db/-0.1dB PB 0 - 31.1 kHz

-3.0dB - 63.2 - kHz

Stopband * 21 SB 145.9 - - kHz

Stopband Attenuation SA 85 - - dB

Group Delay Distortion : 0Hz-40kHz GD - - 0.6 1/fs

Group Delay * 22 GD - 7 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 3.8 - Hz

1-5. Voice Filter (ADxVO bit = “1” (x=1,2)) fs=16kHz

Parameter Symbol Min. Typ. Max. Unit

VOICE

Passband * 21 -0.5dB/0.5dB PB 0 - 6.3 kHz

-3.0dB - 6.9 - kHz

Stopband * 21 SB 8.0 - - kHz

Stopband Attenuation SA 60 - - dB

Group Delay Distortion : 0Hz-8kHz GD - 0 - 1/fs

Group Delay * 22 GD - 20 - 1/fs

ADC Digital Filter(HPF)

Frequency Response -3.0dB FR - 0.3 - Hz

![Page 25: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/25.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 25 -

2. DAC 1~2部

(Ta=-40-85C; AVDD= 3.13-3.6V,TVDD1=TVDD2=TVDD3= 1.7-3.6V, VDD12=1.14-1.3V;AVSS=DVSS=0V;) 2-1 Sharp Roll-Off Filter (DASD bit = “0”, DASL bit = “0”) fs=48kHz

Parameter Symbol Min. Typ. Max. Unit

SHARP ROLL-OFF

Passband * 23 0.05dB PB 0 21.7 kHz

3.0dB PB 23.4 kHz Passband Ripple -0.0032 0.0032 dB

Stopband * 23 26.3 kHz

Stopband Attenuation * 25 * 26 80 dB

Group Delay * 24 - 27.3 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 20.0kHz -0.3 0.1 dB

fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

SHARP ROLL-OFF

Passband * 23 0.05dB PB 0 43.5 kHz 3.0dB PB 46.8 kHz

Passband Ripple PR -0.0032 0.0032 dB

Stopband * 23 SB 52.5 0 kHz

Stopband Attenuation * 25 * 26 SA 80 dB

Group Delay * 24 GD - 27.3 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 40.0kHz -0.5 0.1 dB

fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

SHARP ROLL-OFF

Passband * 23 0.05dB PB 0 87.0 kHz 3.0dB PB 93.6 kHz

Passband Ripple PR -0.0032 0.0032 dB

Stopband * 23 SB 105 kHz

Stopband Attenuation * 25 * 26 SA 80 dB

Group Delay * 24 GD - 27.3 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 80.0kHz -1.9 0.1 dB

Notes

* 23. 通過域、阻止域の周波数はfs(システムサンプリングレート)に比例し、

“PB=0.4535 fs, SB=0.546 fs” です。

* 24. ディジタルフィルタによる演算遅延で、16/20/24/32ビットのインパルスデータが入力レジスタに

セットされてからアナログ信号のピークが出力されるまでの時間です。

* 25. 入力に1kHz、0dBのsine波を与えたときの出力レベルを0dBとします。

* 26. 0kH fsまでの特性です。

![Page 26: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/26.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 26 -

2-2 Slow Roll-Off Filter (DASD bit = “0”, DASL bit = “1”) fs=48kHz

Parameter Symbol Min. Typ. Max. Unit

SLOW ROLL-OFF

Passband * 27 0.05dB PB 0 8.8 kHz 3.0dB PB 19.8 kHz

Passband Ripple -0.043 0.043 dB

Stopband * 23 42.7 kHz

Stopband Attenuation * 25 * 26 73 dB

Group Delay * 24 - 6.8 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 20.0kHz -5.0 0.1 dB

fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

SLOW ROLL-OFF

Passband * 27 0.05dB PB 0 17.7 kHz 3.0dB PB 39.5 kHz

Passband Ripple -0.043 0.043 dB

Stopband * 23 85.3 kHz

Stopband Attenuation * 25 * 26 73 dB

Group Delay * 24 - 6.8 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 40.0kHz -5.2 0.1 dB

fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

SLOW ROLL-OFF

Passband * 27 0.05dB PB 0 35.5 kHz

3.0dB PB 79.0 kHz Passband Ripple -0.043 0.043 dB

Stopband * 23 171 kHz

Stopband Attenuation * 25 * 26 73 dB

Group Delay * 24 - 6.8 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 80.0kHz -5.9 0.1 dB

Note

* 27. 通過域、阻止域の周波数はfs(システムサンプリングレート)に比例し、

“PB=0.185 fs, SB=0.888 fs” です。

![Page 27: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/27.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 27 -

2-3 Short Delay Sharp Roll-Off Filter (DASD bit = “1”, DASL bit = “0”) fs=48kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SHARP ROLL-OFF

Passband * 23 0.05dB PB 0 21.7 kHz

3.0dB PB 23.4 kHz

Passband Ripple -0.0031 0.0031 dB

Stopband * 23 26.3 kHz

Stopband Attenuation * 25 * 26 80 dB

Group Delay * 24 - 6.3 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 20.0kHz -0.3 0.1 dB

fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SHARP ROLL-OFF

Passband * 23 0.05dB PB 0 43.5 kHz

3.0dB PB 46.8 kHz

Passband Ripple -0.0031 0.0031 dB

Stopband * 23 52.5 0 kHz

Stopband Attenuation * 25 * 26 80 dB

Group Delay * 24 - 6.3 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 40.0kHz -0.5 0.1 dB

fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SHARP ROLL-OFF

Passband * 23 0.05dB PB 0 87.0 kHz

3.0dB PB 93.6 kHz

Passband Ripple -0.0031 0.0031 dB

Stopband * 23 105 kHz

Stopband Attenuation * 25 * 26 80 dB

Group Delay * 24 - 6.3 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 80.0kHz -1.9 0.1 dB

![Page 28: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/28.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 28 -

2-4 Short Delay Slow Roll-Off Filter (DASD bit = “1”, DASL bit = “1”) fs=48kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SLOW ROLL-OFF

Passband * 28 0.05dB PB 0 12.0 kHz 3.0dB PB 21.1 kHz

Passband Ripple -0.05 0.05 dB

Stopband * 23 41.5 kHz

Stopband Attenuation * 25 * 26 82 dB

Group Delay * 24 - 5.3 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 20.0kHz -4.8 0.1 dB

fs=96kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SLOW ROLL-OFF

Passband * 28 0.05dB PB 0 24.2 kHz 3.0dB PB 42.1 kHz

Passband Ripple -0.05 0.05 dB

Stopband * 23 83.0 kHz

Stopband Attenuation * 25 * 26 82 dB

Group Delay * 24 - 5.3 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 40.0kHz -5.0 0.1 dB

fs=192kHz

Parameter Symbol Min. Typ. Max. Unit

SHORT DELAY SLOW ROLL-OFF

Passband * 28 0.05dB PB 0 48.4 kHz

3.0dB PB 84.3 kHz Passband Ripple PR -0.05 0.05 dB

Stopband * 23 SB 165.9 kHz

Stopband Attenuation * 25 * 26 SA 82 dB

Group Delay * 24 GD - 5.3 - 1/fs

Digital Filter + SCF + SMF * 25

Frequency Response: 0 80.0kHz -5.7 0.1 dB

Note

* 28 通過域、阻止域の周波数はfs(システムサンプリングレート)に比例し、

“PB=0.252 fs, SB=0.864 fs” です。

![Page 29: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/29.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 29 -

3. SRC 1~8部 (Ta=-40~85°C; AVDD=3.13~3.6V, TVDD1=TVDD2=TVDD3=1.7~3.6V, VDD12=1.14~1.3V; AVSS =DVSS=0V)

3-1. Audioモード(SRCFAUDx bit=”1”, SRCFECx bit=”0”)

* 29. SRCブロック単体での値です。入力と出力の位相ずれがない時の、SRCへデータが入力された後の入力

側LRCKの立ち上がりから、データを出力する前の出力側LRCK立ち上がりまでの時間です。

Parameter Symbol Min. Typ. Max. Unit

通過

域

-0.01dB 0.980≦FSO/FSI≦6.000 PB 0 0.4583FSI kHz

-0.01dB 0.900≦FSO/FSI<0.990 PB 0 0.4167FSI kHz

-0.01dB 0.533≦FSO/FSI<0.909 PB 0 0.2182FSI kHz

-0.01dB 0.490≦FSO/FSI<0.539 PB 0 0.2177FSI kHz

-0.01dB 0.450≦FSO/FSI<0.495 PB 0 0.1948FSI kHz

-0.01dB 0.225≦FSO/FSI<0.455 PB 0 0.1312FSI kHz

-0.50dB 0.167≦FSO/FSI<0.227 PB 0 0.0658FSI kHz

阻止域

0.980≦FSO/FSI≦6.000 SB 0.5417FSI kHz

0.900≦FSO/FSI<0.990 SB 0.5021FSI kHz

0.533≦FSO/FSI<0.909 SB 0.2974FSI kHz

0.490≦FSO/FSI<0.539 SB 0.2812FSI kHz

0.450≦FSO/FSI<0.495 SB 0.2604FSI kHz

0.225≦FSO/FSI<0.455 SB 0.1802FSI kHz

0.167≦FSO/FSI<0.227 SB 0.0970FSI kHz

通過域リップル 0.225≦FSO/FSI≦6.000 PR ±0.01 dB

0.167≦FSO/FSI<0.227 PR ±0.50 dB

阻止域減衰量 0.225≦FSO/FSI≦6.000 SA 95.2 dB

0.167≦FSO/FSI<0.455 SA 85.0 dB

群遅延 (Ts=1/fs)

(* 29)

GD

67 (55/FSI+12/FSO)

Ts

![Page 30: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/30.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 30 -

3-2. Voiceモード(SRCFAUDx=0, SRCFECx=0)

3-3. Echo Cancellerモード(SRCFECx=1)

Parameter Symbol Min. Typ. Max. Unit

通過

域

-0.01dB 0.980≦FSO/FSI≦6.000 PB 0 0.4583FSI kHz

-0.01dB 0.900≦FSO/FSI<0.990 PB 0 0.4167FSI kHz

-0.50dB 0.711≦FSO/FSI<0.910 PB 0 0.3420FSI kHz

-0.50dB 0.653≦FSO/FSI<0.718 PB 0 0.3007FSI kHz

-0.50dB 0.450≦FSO/FSI<0.660 PB 0 0.2230FSI kHz

-0.50dB 0.327≦FSO/FSI<0.455 PB 0 0.1417FSI kHz

-0.50dB 0.225≦FSO/FSI<0.330 PB 0 0.1018FSI kHz

-0.50dB 0.167≦FSO/FSI<0.227 PB 0 0.0658FSI kHz

阻止域

0.980≦FSO/FSI≦6.000 SB 0.5417FSI 0.5417FSI kHz

0.900≦FSO/FSI<0.990 SB 0.5021FSI 0.5021FSI kHz

0.711≦FSO/FSI<0.910 SB 0.3735FSI 0.3735FSI kHz

0.653≦FSO/FSI<0.718 SB 0.3320FSI 0.3320FSI kHz

0.450≦FSO/FSI<0.660 SB 0.2490FSI 0.2490FSI kHz

0.327≦FSO/FSI<0.455 SB 0.1660FSI 0.1660FSI kHz

0.225≦FSO/FSI<0.330 SB 0.1248FSI 0.1248FSI kHz

0.167≦FSO/FSI<0.227 SB 0.0970FSI 0.0970FSI kHz

通過域リップル 0.900≦FSO/FSI≦6.000 PR ±0.01 dB

0.167≦FSO/FSI≦0.910 PR ±0.50 dB

阻止域減衰量

0.900≦FSO/FSI≦6.000 SA 95.2 95.2 dB

0.653≦FSO/FSI<0.909 SA 90.0 90.0 dB

0.450≦FSO/FSI≦0.660 SA 70.0 70.0 dB

0.167≦FSO/FSI<0.455 SA 60.0 60.0 dB

群遅延 (Ts=1/fs)

(* 29)

GD

67 (55/FSI+12/FSO)

Ts

Parameter Symbol Min. Typ. Max. Unit

通過域 -0.01dB 0.167≦FSO/FSI≦6.000 PB 0 0.4583FSI kHz

阻止域 0.167≦FSO/FSI≦6.000 SB 0.5417FSI kHz

通過域リップル 0.167≦FSO/FSI≦6.000 PR ±0.01 dB

阻止域減衰量 0.167≦FSO/FSI≦6.000 SA 95.2 dB

群遅延 (Ts=1/fs)

(* 29)

GD

67 (55/FSI+12/FSO)

Ts

![Page 31: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/31.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 31 -

10. DC特性

(Ta=-40~85°C; AVDD=3.13~3.6V, TVDD1=TVDD2=TVDD3=1.7~3.6V, VDD12=1.14~1.3V; AVSS =DVSS=0V)

Parameter Symbol Min. Typ. Max. Unit

ハイレベル入力電圧1 (* 30) VIH1 80%TVDD1 V

ローレベル入力電圧1 (* 30) VIL1 20%TVDD1 V

ハイレベル入力電圧2 (* 31) VIH2 80%TVDD2 V

ローレベル入力電圧2 (* 31) VIL2 20%TVDD2 V

ハイレベル入力電圧3 (* 32) VIH3 80%TVDD3 V

ローレベル入力電圧3 (* 32) VIL3 20%TVDD3 V

ハイレベル入力電圧A1 (* 33) VIHA1 80%AVDD V

ローレベル入力電圧A1 (* 33) VILA1 20%AVDD V

ハイレベル入力電圧A2 (* 34) VIHA2 65%AVDD V

ローレベル入力電圧A2 (* 34) VILA2 35%AVDD V

SCL, SDAハイレベル入力電圧 VIH4 70%TVDD2 V

SCL, SDAローレベル入力電圧 VIL4 30%TVDD2 V

ハイレベル出力電圧Iout= -100A (* 35) VOH1 TVDD1-0.3 V

ローレベル出力電圧Iout= 100A (* 35) VOL1 0.3 V

ハイレベル出力電圧Iout= -100A (* 36) VOH2 TVDD2-0.3 V

ローレベル出力電圧Iout= 100A (* 36) VOL2 0.3 V

ハイレベル出力電圧Iout= -100A (* 37) VOH3 TVDD3-0.3 V

ローレベル出力電圧Iout= 100A (* 37) VOL3 0.3 V

ハイレベル出力電圧Iout= -100A (* 38) VOHA AVDD3-0.4 V

ローレベル出力電圧Iout= 100A (* 38) VOLA 0.4 V

SCL,SDA

ローレベル

出力電圧

Fast Mode

TVDD2≧2.0V (Iout= 3mA) VOL4 0.4 V

TVDD2<2.0V (Iout= 3mA) VOL4 20%TVDD2 V

入力リーク電流 Iin ±10 A

Notes:

* 30. BICK1, LRCK1, BICK2, LRCK2, SDIN1, SDIN2/JX0 pinに対応します。

* 31. BICK3, LRCK3, BICK4, LRCK4, SDIN3/JX1, SDIN4, CADN/CSN, SELE/SI, SCLK, PDN pinに対応

します。

* 32. BICK5, LRCK5, SDIN5/JX2, SDIN6/JX3 pinに対応します。

* 33. XTI pinに対応します。

* 34. DMDAT1/2 pinに対応します。

* 35. SDOUT1, BICK1, LRCK1, BICK2, LRCK2, SDOUT2/GPO0 pinに対応します。

* 36. SDOUT3/GPO1/SBST, BICK3, LRCK3, LRCK4/CLKO/RDY, BICK4, STO/SDOUT4/RDY, SO pinに

対応します。

* 37. SDOUT5/GPO2/CLKO, LRCK5/CLKO, BICK5, SDOUT6/DIT/GPO3/CLKO pinに対応します。

* 38. DMCLK1/2 pinに対応します。

![Page 32: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/32.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 32 -

11. スイッチング特性

1. システムクロック

(Ta=-40~85°C; AVDD=3.13~3.6V, TVDD1=TVDD2=TVDD3=1.7~3.6V, VDD12=1.14~1.3V; AVSS =DVSS=0V; CL= 20pF)

Parameter Symbol Min. Typ. Max. Unit

XTI Input Timing

a) X’tal Oscillator

Input Frequency fXTI 11.2896 24.576 MHz

b) XTI Clock Input

Duty Cycle 40 50 60 %

Input Frequency fXTI 0.256 24.576 MHz

CLKO Output Timing

Output Frequency fCLKO 2.048 24.576 MHz

Duty Cycle dCLKO 50 %

LRCK/BICK Input Timing (Slave Mode)

LRCK Input Timing

Frequency fs 8 192 kHz

BICK Input Timing

Frequency (* 39) fBCLK 0.256 24.576 MHz

Pulse Width Low tBCLKL 0.4 / fBCLK ns

Pulse Width High tBCLKH 0.4 / fBCLK ns

LRCK/BICK Output Timing (PLL Master Mode)

LRCK Output Timing

Frequency fs 8 192 kHz

Pulse Width High PCM Mode Except PCM Mode

tLRCKH tLRCKH

1/fBCLK

50

ns %

BICK Output Timing

Frequency (* 39) fBCLK 0.256 24.576 MHz

Duty dBCLK 50 %

Note:

* 39. fBCLK ≥ 2 x fs x (入出力データのデータ長)の周波数を満たす必要があります。

![Page 33: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/33.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 33 -

Figure 2. システムクロックタイミング波形

2. パワーダウン

(Ta=-40~85°C; AVDD=3.13~3.6V, TVDD1=TVDD2=TVDD3=1.7~3.6V, VDD12=1.14~1.3V; AVSS =DVSS=0V)

Parameter Symbol Min. Typ. Max. Unit

PDNパルス幅 (* 40) tRST 600 ns

Note:

* 40. 電源投入時はPDN pin = “L”にしてください。

VIL2

tRST

PDN

Figure 3. リセットタイミング波形

1/fXTI 1/fXTI

VIHA1

VILA1 XTI

1/fs

1/fs

tBCLKL tBCLKH

1/fBCLK

1/fBCLK

VIH1/2/3

VIL1/2/3

LRCK1~5

BICK1~5

VIH1/2/3

VIL1/2/3

![Page 34: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/34.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 34 -

3. シリアルデータインタフェース(SDIN1 ~ SDIN6, SDOUT1 ~ SDOUT6)

(Ta=-40~85°C;AVDD=3.13~3.6V,TVDD1=TVDD2=TVDD3=1.7~3.6V, VDD12=1.14~1.3V;AVSS =DVSS=0V; CL=20pF)

Parameter Symbol Min. Typ. Max. Unit

スレーブモード

BICK“↑”からLRCKへの遅延時間 (* 41) tBLRD 10 ns

LRCKからBICK“↑”への遅延時間 (* 41) tLRBD 10 ns

シリアルデータ入力 ラッチセットアップ時間 tBSIDS 10 ns

シリアルデータ入力 ラッチホールド時間 tBSIDH 5 ns

BICK“↓”からシリアルデータ出力遅延時間

(* 42,* 43) tBSOD1 20 ns

BICK“↑”からシリアルデータ出力遅延時間 (* 41) tBSOD2 5 30 ns

マスタモード

BICK周波数 fBCLK 32, 48, 64,128,

256,512 fs

BICKデューティ比 50 %

BICK“↓”からLRCKへの遅延時間 (* 42) tMBL -10 10 ns

シリアルデータ入力 ラッチセットアップ時間 tBSIDS 20 ns

シリアルデータ入力 ラッチホールド時間 tBSIDH 10 ns

BICK“↓”からシリアルデータ出力遅延時間

(* 42,* 43) tBSOD 10 ns

Notes:

* 41. レジスタBCKPx bit = “1”でBICKの極性を反転させた場合は、BICKの“↓”からになります。

* 42. レジスタBCKPx bit = “1”でBICKの極性を反転させた場合は、BICKの“↑”からになります。

* 43. スレーブモード動作時、サンプリング周波数96kHz且つTDM256モードで出力する場合のように

BICKxが12.288MHzよりも高速動作する場合は、SDOPHx bit = “1”に設定して、BICK “↑”基準で

データを出力してください。マスタモード動作時は、SDOPHx bit = “0”で使用して下さい。

![Page 35: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/35.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 35 -

1. スレーブモード

tBSIDS

tBLRD tLRBD

D

VIH 1/2/3

D VIL 1/2/3

D

tBSIDH

SDIN1 ~ 6

LRCK(I)

BICK(I) VIH 1/2/3

D VIL 1/2/3

D VIH 1/2/3

D VIL 1/2/3

D Figure 4. スレーブモード時 シリアルインタフェース入力タイミング波形

VIH 1/2/3 LRCK(I)

BICK(I)

VIL 1/2/3

SDOUT1~6 50%TVDD1/2/3

tBSOD1

D

VIH 1/2/3

VIL 1/2/3

tBLRD tLRBD

D

tBSOD1

D

Figure 5. スレーブモード時 シリアルインタフェース出力タイミング波形 (SDOPHx bit = “0”)

VIH 1/2/3 LRCK(I)

BICK(I)

VIL 1/2/3

SDOUT1~6 50%TVDD1/2/3

tBSOD2

D

VIH 1/2/3

VIL 1/2/3

tBLRD tLRBD

D

tBSOD2

D

Figure 6. スレーブモード時 シリアルインタフェース出力タイミング波形 (SDOPHx bit = “1”)

![Page 36: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/36.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 36 -

2. マスタモード

tBSIDS

tMBL tMBL

D

LRCK(O)

BICK(O)

VIH 1/2/3

D VIL 1/2/3

tBSIDH

SDIN1 ~ 6

50%TVDD1/2/3

50%TVDD1/2/3

Figure 7. マスタモード時 シリアルインタフェース入力タイミング波形

tBSOD

D

LRCK(O)

BICK(O)

SDOUT1~6

50%TVDD1/2/3

50%TVDD1/2/3

50%TVDD1/2/3

tBSOD

D

Figure 8. マスタモード時 シリアルインタフェース出力タイミング波形

![Page 37: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/37.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 37 -

4. SPIインタフェース

(Ta=-40~85°C; AVDD=3.13~3.6V, TVDD1=TVDD2=TVDD3=1.7~3.6V, VDD12=1.14~1.3V; AVSS =DVSS=0V; CL= 20pF)

1. SPI低速モード (CKRESETN bit = “0”)

Parameter Symbol Min. Typ. Max. Unit

マイコンインタフェース用信号

SCLK 周波数 (* 45) fSCLK 3.5 MHz

SCLK ローレベル幅 tSCLKL 135 ns

SCLK ハイレベル幅 tSCLKH 135 ns

マイコン→本製品

CSNハイレベル幅 tWRQH 300 ns

CSN “↑” からPDN “↑” tRST 360 ns

PDN “↑”からCSN “↓” tIRRQ 1 ms

CSN “↓”からSCLK “↓” tWSC 300 ns

SCLK “↑”からCSN “↑” tSCW 480 ns

SI ラッチセットアップ時間 tSIS 120 ns

SI ラッチホールド時間 tSIH 120 ns

本製品→マイコン

SCLKの“↓”からSO出力遅延時間 tSOS 120 ns

SCLKの“↑”からSO出力ホールド時間 (* 44) tSOH 120 ns

2. SPI高速モード (CKRESETN bit = “1”かつPLLがロック)

Parameter Symbol Min. Typ. Max. Unit

マイコンインタフェース用信号

SCLK 周波数 (* 45) fSCLK 7 MHz

SCLK ローレベル幅 tSCLKL 60 ns

SCLK ハイレベル幅 tSCLKH 60 ns

マイコン→本製品

CSNハイレベル幅 tWRQH 150 ns

CSN “↑” からPDN “↑” tRST 180 ns

PDN “↑”からCSN “↓” tIRRQ 1 ms

CSN “↓”からSCLK “↓” tWSC 150 ns

SCLK “↑”からCSN “↑” tSCW 240 ns

SI ラッチセットアップ時間 tSIS 60 ns

SI ラッチホールド時間 tSIH 60 ns

本製品→マイコン

SCLKの“↓”からSO出力遅延時間 tSOS 60 ns

SCLKの“↑”からSO出力ホールド時間 (* 44) tSOH 60 ns

Note:

* 44. コマンドコードの24bit (コマンド8bit + アドレス16bit)目入力時は除きます。書き込み準備データ

読み出しコマンド0x24,0x26,0x28の場合は8bit(コマンド8bit)目になります。

* 45. I2CからSPIインタフェースに切り替えるためのダミーコマンドの発行、コントロールレジスタへの

アクセスは常にSPI高速モード(Max. 7MHz)で行えます。DSPのRAM領域へのアクセスはクロック

リセット(CKRESETN bit =”0”)時、SPI低速モード(Max. 3.5MHz)、PLLロック(CKRESETN bit = “1”

かつPLLがロック)時、SPI高速モード(Max. 7MHz)で行えます。また、PLLアンロック時、DSPの

RAM領域にアクセスする際、DLRDY bitを”1”に設定する必要があります。CKRESETN bit = “0”→ “1”

設定後、PLLがロックするまでには最大10msかかります。

![Page 38: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/38.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 38 -

tSCLKH

tSCLKL

1/fSCLK

1/fSCLK

SCLK

VIH2 VIL2

VIH2

VIL2

VIH2

VIL2

tRST

PDN

CSN

tIRRQ

Figure 9. SPIインタフェースタイミング波形1

tWRQH

tSIS

tSIH

tSCW tSCW tWSC tSCW

CSN

SI VIH2

VIL2

VIH2

tWSC

SCLK VIL2

VIH2

VIL2

Figure 10. SPIインタフェースタイミング波形2(マイコン→ 本製品)

tSOS

tSOH

SCLK VIL2

VIH2

SO VIH2

VIL2

Figure 11. SPIインタフェースタイミング波形3(本製品→マイコン)

![Page 39: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/39.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 39 -

5. I2Cインタフェース

(Ta=-40~85°C; AVDD=3.13~3.6V, TVDD1=TVDD2=TVDD3=1.7~3.6V, VDD12=1.14~1.3V; AVSS =DVSS=0V; CL= 20pF)

<I2C: Fast Mode>

Parameter Symbol Min. Typ. Max. Unit

I2C Timing

SCL clock frequency fSCL - - 400 kHz

Bus Free Time Between Transmissions tBUF 1.3 - - s

Start Condition Hold Time (prior to first Clock pulse) tHD:STA 0.6 - - s

Clock Low Time tLOW 1.3 - - s

Clock High Time tHIGH 0.6 - - s

Setup Time for Repeated Start Condition tSU:STA 0.6 - - s

SDA Hold Time from SCL Falling tHD:DAT 0 - - s

SDA Setup Time from SCL Rising tSU:DAT 0.1 - - s

Rise Time of Both SDA and SCL Lines tR - - 0.3 s

Fall Time of Both SDA and SCL Lines tF - - 0.3 s

Setup Time for Stop Condition tSU:STO 0.6 - - s

Pulse Width of Spike Noise Suppressed By Input Filter tSP 0 - 50 ns

SDA Data Valid Time from SCL Falling tVD:DAT - - 0.9 s

Capacitive load on bus Cb - - 400 pF

tHIGH

SCL

SDA VIH4

tLOW tBUF

tHD:STA

tR tF

tHD:DAT tSU:DAT tSU:STA

Stop Start Start Stop

tSU:STO

VIL4

VIH4

VIL4

tSP

Figure 12. I2C BUSインタフェースタイミング波形

![Page 40: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/40.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 40 -

6. デジタルマイクインタフェース

(Ta=-40~85C; AVDD=3.13~3.6V, TVDD1=TVDD2=TVDD3=1.7~3.6V, VDD12=1.14~1.3V; AVSS=DVSS=0V; CL=100pF)

Parameter Symbol Min. Typ. Max. Unit

DMDAT

シリアルデータ入力 ラッチセットアップ時間 tDMDS 50 ns

シリアルデータ入力 ラッチホールド時間 tDMDH 0 ns

DMCLK

クロック周波数 (* 46) fDMCK 0.5 64fs 6.2 MHz

デューティ比 dDMCK 40 50 60 %

立ち上がり時間 tDMCKR 10 ns

立ち下がり時間 tDMCKF 10 ns

Notes:

* 46. クロック周波数は、FSMODE[4:0] bitsで選択されたサンプリングレート(fs)で決まります。

tDMCK

65%AVDD

DMCLK1/2 35%AVDD

tDMCKL

50%AVDD

fDMCK = 1 / tDMCK dDMCK = 100 x tDMKL / tDMCK

tDMCKR tDMCKF

DMCLK1/2 50%AVDD

DMDAT1/2

tDMDS

VIHA2

VILA2

tDMDH

DMCLK1/2 50%AVDD

DMDAT1/2

tDMDS

VIHA2

VILA2

tDMDH

DCLKP1/2 bit =”1”

DCLKP1/2 bit =”0”

Figure 13. ディジタルマイクインタフェースタイミング波形

![Page 41: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/41.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 41 -

7. Master SPIインタフェース

(Ta=-40~85°C; AVDD=3.13~3.6V, TVDD1=TVDD2=TVDD3=1.7~3.6V, VDD12=1.14~1.3V; AVSS =DVSS=0V; CL= 20pF)

Parameter Symbol Min. Typ. Max. Unit

Master Mode

SCLK周波数 -

6.144 MHz

SCLK Duty比 (* 47) - 50

ECSO ↓からESCLK↑ - 80 ns

Delay Time from ESCLK↓ to ESDO - -40 40 ns

ESDI Hold Time from ESCLK ↑ - 40 ns

ESDI Setup Time from ESCLK ↑ - 40 ns

Through Mode

Slave Port → Master Port

CSN入力からECSO 出力遅延時間 - 0 40 ns

SCLK入力からESCLK 出力遅延時間 - 0 40 ns

SI入力からESDO 出力遅延時間 - 0 40 ns

Master Port → Slave Port

ESDI入力からSO 出力遅延時間 - 0 40 ns

* 47. 分周数偶数時

セルフブート利用時は12.288MHz以下の水晶発振器に対応しています。

![Page 42: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/42.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 42 -

12. 外部接続回路例

■ 接続図

SDOUT3/GPO1 27

41

SO SCLK 39

38 μP

63

12 Digital IO 1.8~3.3V

PDN

TVDD1

RESET CONTROL

AK7739

VREFH

10

Audio I/F

0.1

CLOCK CSN 37

& 36

STO/SDOUT4/RDY

SDIN3/JX1 28

61 Analog +3.3V

AVDD 10 0.1

VCOM 60

2.2

DVSS 13,34,20

33 Digital IO 1.8~3.3V TVDD2

10 0.1

19 Digital IO 3.3V TVDD3

10 0.1

5,25,42 Digital Core 1.2V VDD12

10 0.1

VREFL

AVSS

DVSS

3 AOUT1R 2 AOUT1L 1

AOUT2L

AOUT2R 4

SI 40 SDIN4 35

LRCK3 29

BICK3/JX3 30

LRCK4/CLKO/RDY 31

BICK4 32

SDOUT1 8

SDIN1 7

SDIN2/JX0 11

SDOUT2/GPO0 14

LRCK1 10

BICK1 9

LRCK2 16

BICK2 15

SDOUT5/GPO2/CLKO 21

SDIN5/JX2 SDIN6/JX3 17

SDOUT6/DIT/GPO3/CLKO 24

LRCK5/CLKO 22

BICK5 23

Audio I/F

CLOCK

&

Audio I/F

CLOCK

&

18

6,26,43

64

62

56 AIN2LP/AIN3L

55 AIN2LN/AIN4L

58 AIN2RP/AIN3R

59 AIN2RN/AIN4R

52 AIN1L/INP1

51 INN1

53 AIN1R/INP2

54 INN2

50

49 MPWR1

MPWR2

MPREF 48

1

2kΩ 2kΩ

2kΩ

2kΩ

10 0.1

1

1 1 1

100n

100n

100n

100n

XTO

XTI

Rd

45

44

46 Analog +3.3V AVDD

10 0.1 AVSS 47

1

1

1

1

Figure 14. SPIインタフェース時の接続例

![Page 43: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/43.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 43 -

■ 周辺回路

1. グラウンド

各VSSは、同電位になるように接続してください。デカップリングコンデンサ、特に小容量のセラミッ

クコンデンサは本製品の近くで接続して下さい。

2. 基準電圧

VCOM pinは AVDD/2電圧を出力しており、アナログ信号のコモン電圧として使われます。高周波ノイ

ズを除去するために、2.2F程度のコンデンサを AVSSとの間に接続して下さい。

VCOM pinは外部回路には使用しないでください。また、ディジタル信号、特にクロック信号は変調器

へのカップリングを避けるため VCOM pinからできるだけ離して下さい。

3. アナログ入力

アナログ入力信号はアナログ変調器に入力されます。差動入力ピンにおけるフルスケール入力電圧は、

FS=±(AVDDAVSS)×0.86 です。シングルエンド入力ピンにおけるフルスケール入力電圧は、

FS=(AVDDAVSS)×0.86です。AVDD=3.3V、AVSS=0.0Vのとき、差動入力ピンにおけるフルスケール

入力電圧は±2.83Vpp(typ)、シングルエンド入力ピンにおけるフルスケール入力電圧は 2.83Vpp(typ)にな

ります。ディジタル出力コードのフォーマットは 2’s complement(2 の補数)です。DC オフセットは内

蔵の HPFでキャンセルされます。

アナログ入力ピンにはパワーダウン解除後に AVDD/2の内部動作点が生成されます。内部動作点生成回

路は各入力ピンに対して 25kΩ (typ.)の内部インピーダンスを持ちます。各入力ピンに DC成分除去用コ

ンデンサを接続する場合には内部インピーダンスとの時定数で内部動作点が立ち上がります。

アナログ変調器は fs=48kHz,96kHz,192kHz のとき 6.144MHz でアナログ入力をサンプリングします。

本製品は AAF (アンチ・エリアシング・フィルタ)を持っており、ADC 入力前に外部でローパスフィル

タを通過させる必要はありません。しかし D/Aコンバータ変換後のオーディオ信号など、帯域外ノイズ

の大きな信号を入力する場合には、外部でローパスフィルタを通過させることを推奨します。

本製品のアナログ電源電圧は+3.3V(typ)であり、アナログ入力ピンには、AVDD+0.3V 以上、AVSS0.3V

以下の電圧と、10mA以上の電流を入力してはいけません。過大電流の流入は、内部の保護回路の破壊、

さらにはラッチアップを引き起こし、ICの破壊に至ります。従って、周辺のアナログ回路の電圧が±15V

等の場合はアナログ入力ピンを絶対最大定格以上の信号から保護する必要があります。

Op Amp

INP*

10k

10k

10k

10k

INN*

Signal

+

- -

+

2.83Vpp

2.83Vpp

+10V

1

1

+

+

-10V

22

+

68p

68p

Figure 15. fs=48kHz時の入力バッファ回路例 (差動入力)

![Page 44: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/44.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 44 -

4. アナログ出力

ラインアウト出力はシングルエンド出力です。出力レンジは VCOM電圧を中心に 0.86xAVDD Vpp (typ)

です。入力コードのフォーマットは、2’s compliment (2の補数)で、0x7FFFFFFF (@32bit)に対しては

正のフルスケール、0x80000000 (@32bit)に対しては負のフルスケール、0x00000000 (@32bit)での理想

値は VCOM電圧が出力されます。VCOM電圧は AVDD/2 (typ)です。ΔΣ変調器が発生する帯域外ノイ

ズ (シェーピングノイズ)は、内蔵のスイッチトキャパシタフィルタ (SCF)と、連続フィルタ (CTF)で

除去されます。

5. ディジタル回路との接続

ディジタル回路によるノイズを最小限に抑えるために、ディジタル出力にはCMOSロジック、または低

電圧ロジックを接続します。

6. 水晶振動子

本製品のXTI pin及びXTO pinに接続する水晶振動子は、発振余裕度の観点から、以下の等価回路パラメ

ータを満たすもの、XTI、XTO各 pinに接続する容量は以下の値で使用することを推奨します。

Table 2. 水晶振動子接続時の推奨抵抗と容量

XTAL

発振周波数 R1 (Max.) C0 (Max.)

XTI, XTO pin

接続容量

12.288MHz 80Ω 2.5pF 22pF

18.432MHz 80Ω 2.5pF 22pF

24.576MHz 40Ω 2.5pF 15pF

Figure 16. 水晶振動子の電気的等価回路

![Page 45: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/45.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 45 -

13. パッケージ

■ 外形寸法図

64-pin HTQFP (Unit: mm)

■ 材質・メッキ仕様

パッケージ材質: エポキシ系樹脂

リードフレーム材質: 銅

端子処理: 半田(無鉛)メッキ

![Page 46: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/46.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 46 -

■ マーキング

1) pin #1 indication 2) Date Code: XXXXXXX(7 digits) 3) Marking Code: AK7739VQ 4) Asahi Kasei Logo

14. オーダリングガイド

■ オーダーリングガイド

AK7739VQ -40 +85ºC 64-pin HTQFP (0.5mm pitch)

AKD7739 AK7739評価ボード

15. 改定履歴

Date (Y/M/D) Revision Reason Page Contents

18/12/03 00 初版

AK7739VQ XXXXXXX

AKM

![Page 47: AK7739 Japanese Datasheet - Product Brief - …...[AK7739] 018013127-J-00-PB 2018/12 - 1 - 1. 概 要 AK7739はマイクアンプ付の24bitステレオADC,入力セレクタ付の24bitステレオADC,4chの32bit](https://reader033.fdocuments.nl/reader033/viewer/2022042606/5f837eac2042e84a7e0801ba/html5/thumbnails/47.jpg)

[AK7739]

018013127-J-00-PB 2018/12 - 47 -

旭化成エレクトロニクス製品のご検討ありがとうございます。

より詳しい資料を用意しておりますので、お手数ですが弊社営業担

当、あるいは弊社特約店営業担当までお申し付けください。

重要な注意事項

0. 本書に記載された弊社製品(以下、「本製品」といいます。)、および、本製品の仕様につ

きましては、本製品改善のために予告なく変更することがあります。従いまして、ご使用を

検討の際には、本書に掲載した情報が最新のものであることを弊社営業担当、あるいは弊社

特約店営業担当にご確認ください。

1. 本書に記載された情報は、本製品の動作例、応用例を説明するものであり、その使用に際し

て弊社および第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うも

のではありません。お客様の機器設計において当該情報を使用される場合は、お客様の責任

において行って頂くとともに、当該情報の使用に起因してお客様または第三者に生じた損害

に対し、弊社はその責任を負うものではありません。

2. 本製品は、医療機器、航空宇宙用機器、輸送機器、交通信号機器、燃焼機器、原子力制御用

機器、各種安全装置など、その装置・機器の故障や動作不良が、直接または間接を問わず、

生命、身体、財産等へ重大な損害を及ぼすことが通常予想されるような極めて高い信頼性を

要求される用途に使用されることを意図しておらず、保証もされていません。そのため、別

途弊社より書面で許諾された場合を除き、これらの用途に本製品を使用しないでください。

万が一、これらの用途に本製品を使用された場合、弊社は、当該使用から生ずる損害等の責

任を一切負うものではありません。

3. 弊社は品質、信頼性の向上に努めておりますが、電子製品は一般に誤作動または故障する場

合があります。本製品をご使用頂く場合は、本製品の誤作動や故障により、生命、身体、財

産等が侵害されることのないよう、お客様の責任において、本製品を搭載されるお客様の製

品に必要な安全設計を行うことをお願いします。

4. 本製品および本書記載の技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、ある

いはその他軍事用途の目的で使用しないでください。本製品および本書記載の技術情報を輸

出または非居住者に提供する場合は、「外国為替および外国貿易法」その他の適用ある輸出

関連法令を遵守し、必要な手続を行ってください。本製品および本書記載の技術情報を国内

外の法令および規則により製造、使用、販売を禁止されている機器・システムに使用しない

でください。

5. 本製品の環境適合性等の詳細につきましては、製品個別に必ず弊社営業担当までお問合せく

ださい。本製品のご使用に際しては、特定の物質の含有・使用を規制するRoHS指令等、適

用される環境関連法令を十分調査のうえ、かかる法令に適合するようにご使用ください。お

客様がかかる法令を遵守しないことにより生じた損害に関して、弊社は一切の責任を負いか

ねます。

6. お客様の転売等によりこの注意事項に反して本製品が使用され、その使用から損害等が生じ

た場合はお客様にて当該損害をご負担または補償して頂きますのでご了承ください。

7. 本書の全部または一部を、弊社の事前の書面による承諾なしに、転載または複製することを

禁じます。