Naar een opgaven gestuurde organisatie: Samen meer realiseren

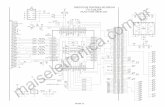

Ontwerp van een volledig ge ntegreerde PWM-gestuurde H ...

Transcript of Ontwerp van een volledig ge ntegreerde PWM-gestuurde H ...

Faculteit Ingenieurswetenschappen

Vakgroep Elektronica en Informatiesystemen

Voorzitter: Prof. Dr. Ir. J. Van Campenhout

Ontwerp van een volledig geıntegreerde

PWM-gestuurde H-brug met IGBT’s

voor de snelheidsregeling van DC-motoren

door

Rik Verplancke

en

Jeroen Missinne

Promotor: Prof. Dr. Ir. J. Doutreloigne

Scriptiebegeleiders: Dr. B. Bakeroot, Ir. V. De Gezelle

Scriptie ingediend tot het behalen van de academische graad van

Burgerlijk Elektrotechnisch Ingenieur:

optie Elektronische Circuits en Systemen

Academiejaar 2006–2007

Voorwoord

In hedendaagse toestellen is elektronica bijna niet meer weg te denken, hoewel ze soms niet

zichtbaar aanwezig is. Een moderne auto heeft bijvoorbeeld tal van systemen aan boord om

de gewenste functionaliteit en veiligheid te garanderen. Het is in dit kader dat het werk zich

situeert.

Deze scriptie heeft als doel een volledig elektronisch systeem te ontwerpen en is dus vooral

van praktische aard. Daarbij was het echter vaak nodig om onderzoek te doen om bepaalde

problemen op een zo goed mogelijke manier op te lossen. Enerzijds werd gebruik gemaakt

van bestaande resultaten, maar anderzijds hebben we zelf ook veel nieuwe circuits ontworpen.

Dit zou uiteraard niet mogelijk geweest zijn zonder de hulp van een aantal personen.

Eerst en vooral zouden we onze promotor Jan Doutreloigne en thesisbegeleiders Benoit Ba-

keroot en Vincent De Gezelle willen bedanken omdat ze altijd onmiddellijk beschikbaar waren

om ons te ontvangen in Zwijnaarde en onze vragen te beantwoorden. Bovendien willen we

nog eens speciaal een woordje van dank uitspreken voor dit mooi thesisonderwerp. Na het

Hardware-ontwerp project van vorig jaar zijn we echt warm geworden voor de materie en dit

enthousiasme is tijdens het uitvoeren van de thesis zeker niet afgenomen. Het was niet altijd

even gemakkelijk, we zijn op veel problemen gestoten en er kroop veel meer tijd in de thesis

dan we aanvankelijk gedacht hadden. We zijn er echter altijd blijven in geloven en hebben

iedere nieuwe dag vol ‘goesting’ en met een glimlach ingezet.

i

ii

Verder willen we ook een dankwoord richten tot Herbert De Pauw en Wim Meews om ons

raad te geven i.v.m. de I3T80 technologie of ons te helpen wanneer Cadence weer zijn grillen

had. Ook zouden we iedereen van de onderzoeksgroep TFCG Microsystems willen bedanken

voor de goede sfeer aldaar.

Ten slotte willen we iedereen bedanken die op welke manier ook een bijdrage geleverd heeft

om dit werk mogelijk te maken en niet met naam vernoemd is. Speciale dank gaat hierbij uit

naar onze ouders, familie, vrienden en medestudenten.

Rik Verplancke en Jeroen Missinne, juni 2007

Toelating tot bruikleen

“De auteurs geven de toelating deze scriptie voor consultatie beschikbaar te stellen en delenvan de scriptie te kopieren voor persoonlijk gebruik.Elk ander gebruik valt onder de beperkingen van het auteursrecht, in het bijzonder met be-trekking tot de verplichting de bron uitdrukkelijk te vermelden bij het aanhalen van resultatenuit deze scriptie.”

Rik Verplancke en Jeroen Missinne, juni 2007

iii

Ontwerp van een volledig geıntegreerde

PWM-gestuurde H-brug met IGBT’s

voor de snelheidsregeling van DC-motoren

door

Rik Verplancke

en

Jeroen Missinne

Scriptie ingediend tot het behalen van de academische graad van

Burgerlijk Elektrotechnisch Ingenieur:

optie Elektronische Circuits en Systemen

Academiejaar 2006–2007

Promotor: Prof. Dr. Ir. J. Doutreloigne

Scriptiebegeleiders: Dr. B. Bakeroot, Ir. V. De Gezelle

Faculteit Ingenieurswetenschappen

Universiteit Gent

Vakgroep Elektronica en Informatiesystemen

Voorzitter: Prof. Dr. Ir. J. Van Campenhout

Samenvatting

In deze thesis wordt voor de eerste maal een volledig monolithisch geıntegreerde elektronischeschakeling rond nieuw ontworpen IGBT’s gebouwd. Hierbij wordt een circuit uitgedachtom deze IGBT’s in een H-brug configuratie aan te sturen, met behulp van een op maatontworpen levelshifter. Uiteindelijk zal deze H-brug dienen om een kleine DC-motor aan tedrijven. Door gebruik te maken van PWM technieken en feedback voor de aansturing vande H-brug, wordt ervoor gezorgd dat de snelheid van de motor in beide richtingen geregeldkan worden onafhankelijk van de belasting. Om de IGBT’s te beschermen werden ook eenaantal protectiecircuits aangebracht. Enerzijds is er een systeem voorzien om de dissipatiein de vermogenscomponenten te begrenzen. Anderzijds zorgt een thermische sensor voor hetveilig uitschakelen indien de temperatuur toch nog te hoog zou oplopen.

Trefwoorden

H-brug, IGBT, snelheidsregeling, AMI Semiconductor I3T80 Technologie, levelshifter

Design of a fully integrated PWM-controlledH-bridge with IGBT’s for the speed control of

DC-motorsJeroen Missinne & Rik Verplancke

Supervisor(s): Jan Doutreloigne, Benoit Bakeroot, Vincent De Gezelle

Abstract—In this article, a system is introduced to control the speed of aDC-motor using insulated gate bipolar transistors (IGBT’s) as switching el-ements in an H-bridge configuration. A fully integrated system has been de-signed using a Smart Power technology, the 80 V 0, 35 µm I3T (ImprovedIntelligent Interface Technology) [1].

Keywords—H-bridge, IGBT, speed control, DC-motor, Smart Power, I3T

I. INTRODUCTION

MODERN electronics have a need for components that dis-sipate less power, without giving in on other performance

parameters. It also has become a trend to integrate an au-tonomous microsystem on a single chip [2]. These so calledSmart Power technologies are used in automotive applicationsor for industrial control.

Recently, IGBT’s have been developed at the TFCG Mi-crosystems Lab and these have been proven promising for theuse in these technologies. However, these components havenever been used in a fully integrated circuit. Therefore, a com-plete system for the speed control of a DC-motor has been de-signed using these IGBT’s in an H-bridge configuration.

A digital circuit generates PWM pulses for the speed controlof a DC-motor, driven by the H-bridge. Several additional cir-cuits are integrated to protect the system against overheating.

II. IGBT

Classical IGBT’s have a few drawbacks. These componentssuffer from latch-up and cannot be used in circuits requiring awide safe operating area. Moreover, the substrate current injec-tion and possible crosstalk with nearby CMOS logic or analogcomponents, makes the integration in Smart Power technologiesdifficult. The proposed IGBT’s try to overcome these problemsusing the standard I3T80 process mask set [3],[4],[5].

III. DESCRIPTION OF THE SYSTEM

A block diagram of the realised system is shown in fig. 1.

A. PWM pulse generation

PWM pulses are generated by comparing a triangular waveand 2 reference levels in a digital way (fig. 2). Using a triangu-lar wave (instead of a sawtooth), generated by an up-and-downcounter, facilitates the introduction of a dead time between thecomplementary PWM pulses.

(a) Speed control & PWM pulse generation

(b) Levelshifter & H-bridge

Fig. 1. Block diagram of the entire system

B. Levelshifter

The H-bridge consists of 4 n-type IGBT’s. Therefore, thePWM pulses have to be shifted to the correct level before theycan drive the high-side IGBT’s as these require a gate signalexceeding the supply voltage. A levelshifter performs this oper-ation.

The basic configuration of the proposed levelshifter is shownin fig. 3.

A common problem with this configuration is the need oflarge bias currents to enable a fast charging of IGBT2’s gateelectrode. Therefore a large capacitor (in the order of nF) isneeded. To avoid the use of such a large component on chip andto enable monolithic integration, this basic configuration wasfully revised. Small bias currents are used in the levelshifter,which necessitates an extra circuit for fast switching. Althoughthe specifications for this levelshifter were quite elementary,they resulted in a complex and time demanding design.

C. Speed control

A configuration for speed control was modeled in Matlab, andafterwards digitally implemented in hardware.

This controller adapts the duty ratio δ of the PWM pulses

Fig. 2. Digital PWM pulse generation

Fig. 3. Basic configuration levelshifter

based on the error signal ε = vdesired − vreal. The speed isrepresented as a digital number between 0 and 511. In orderto regulate the actual speed, the duty ratio δ is corrected with avalue of sgn(ε) Λ

512 , resulting in a correct working digital feed-back system. Λ is defined through (1).

ε = 0 : Λ = 0|ε| ∈ [1, 7] : Λ = 1

|ε| ∈ [8, 511] : Λ =⌊

|ε|2

⌋ (1)

D. Current limitation & thermal protection

The H-bridge is dimensioned for current levels up to 0, 5 A.A circuit is present to limit load currents, and consequently thedissipation of the switching elements. However, if the tem-perature still rises too much, a thermal protection circuit shutsthe system down at 150 C.

IV. SIMULATION RESULTS

An example of a simulation of the complete system as per-formed in Cadence (an electrical simulator), is shown in fig. 4.

First, the desired value for the speed was set at 3500 Rpm.The simulation result shows that the motor reaches its set pointafter a transient period. At t = 30 ms, the target value of thespeed was changed to −2000 Rpm and the motor speed followsthe changing set point.

Before reaching its final value of 3500 Rpm, the motor speedshows an overshoot, as expected. Because of the current limi-

Fig. 4. Simulation of the entire system

tation circuit in the H-bridge, the motor has a slower speed ofreaction, causing overshoot in a number of situations.

V. CONCLUSIONS

A system for speed control of a DC-motor was presented,combining digital, analog and power electronics on a singlechip. Recently developed IGBT’s were used as switching ele-ments in a H-bridge. Extensive simulations have proven that thespeed control system is working as intended.

ACKNOWLEDGMENTS

The authors would like to thank our supervisors JanDoutreloigne, Benoit Bakeroot and Vincent De Gezelle for theirsupport throughout the year.

REFERENCES

[1] P. Moens, D. Bolognesi, L. Delobel, D. Villanueva, H. Hakim, S.C. Trinh,K. Reynders, F. De Pestel, A. Lowe, E. De Backer, G. Van Herzeele, andM Tack. I3T80: a 0.35 µm based system-on-chip technology for 42 v bat-tery automotive applications. In Proceedings of the International Sympo-sium Power Semiconductor Devices and ICs, pages 225 – 228, 2002.

[2] Jan Doutreloigne. Microsystem Design. Course at the University of Ghent.[3] B. Bakeroot, J. Doutreloigne, and P. Moens. A new ligbt structure to sup-

press substrate currents in a junction isolated technology. Solid-State Elec-tronics, 49(3):363–367, 2005.

[4] B. Bakeroot, J. Doutreloigne, and P. Moens. An Ultrafast Floating 75 VLateral IGBT with a Buried Hole Diverter and an Effective Junction Isola-tion. IEEE Electron Device Letters, 27(6):492–494, 2006.

[5] B. Bakeroot, J. Doutreloigne, P. Vanmeerbeek, and P. Moens. A new lateral-igbt structure with a wider safe operating area. IEEE Electron Device Let-ters, 28(5):416–418, 2007.

Inhoudsopgave

Overzicht iv

Extended abstract v

Inhoudsopgave vii

Gebruikte afkortingen xi

1 Inleiding 11.1 Kader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.2 Probleemstelling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.3 Doelstelling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2 Principe van een PWM-gestuurde H-brug 42.1 H-brug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.1.1 Aansturing van een H-brug . . . . . . . . . . . . . . . . . . . . . . . . 52.1.2 Inductieve last . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52.1.3 Aansturen van een motor . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.2 PWM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.3 IGBT’s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3 IGBT’s 93.1 IGBT’s in de I3T80 technologie van AMIS . . . . . . . . . . . . . . . . . . . . 9

3.1.1 Klassieke n-LIGBT structuur . . . . . . . . . . . . . . . . . . . . . . . 93.1.2 Verbeterde n-LIGBT structuur . . . . . . . . . . . . . . . . . . . . . . 11

3.2 Elektrische karakteristieken van de IGBT . . . . . . . . . . . . . . . . . . . . 143.2.1 De IGBT in DC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143.2.2 Safe Operating Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163.2.3 Schakelgedrag van een igbt . . . . . . . . . . . . . . . . . . . . . . . . 16

vii

Inhoudsopgave viii

4 Generatie van PWM-pulsen 204.1 Inleiding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.2 Principe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.3 Realisatie van de verschillende bouwblokken . . . . . . . . . . . . . . . . . . . 21

4.3.1 Gemodificeerde teller . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214.3.2 Klok ter aansturing van de gemodificeerde teller . . . . . . . . . . . . 224.3.3 Sommatie-circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274.3.4 Comparator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.4 Globaal schema . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284.5 Resultaten . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304.6 Werking bij hogere frequenties . . . . . . . . . . . . . . . . . . . . . . . . . . 30

5 Aansturing van de uitgangstrap met behulp van een levelshifter 325.1 Inleiding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325.2 Principeschema . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.2.1 Werking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335.2.2 Specificaties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 365.2.3 Problemen bij het principeschema . . . . . . . . . . . . . . . . . . . . 37

5.3 Ontworpen schema . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 375.3.1 De regime-tak . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385.3.2 De ontlaad-tak . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425.3.3 De laad-tak . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.4 Resultaten . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 555.4.1 Simulatieresultaten van de levelshifter met inductieve last (motor) . . 555.4.2 Robuustheid van het ontwerp . . . . . . . . . . . . . . . . . . . . . . . 595.4.3 Specificaties van het ontwerp . . . . . . . . . . . . . . . . . . . . . . . 61

6 De H-brug met protectiecircuits 646.1 Inleiding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 646.2 Stroombegrenzing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.2.1 Werking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 646.2.2 Dimensionering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 666.2.3 Resultaten . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

6.3 Thermisch protectiecircuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 696.3.1 Principe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 696.3.2 Temperatuursensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 696.3.3 Geconditioneerde temperatuursensor . . . . . . . . . . . . . . . . . . . 726.3.4 Toegepaste thermische beveiliging . . . . . . . . . . . . . . . . . . . . 74

Inhoudsopgave ix

7 Snelheidsregeling 777.1 Inleiding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 777.2 Terugkoppelen van de snelheid . . . . . . . . . . . . . . . . . . . . . . . . . . 777.3 Regelen van de snelheid . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

7.3.1 Regelaar . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 797.3.2 Geheugen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 817.3.3 Feedback-klok . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

7.4 Bypass-circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 857.5 Resultaten . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 857.6 Werking bij hogere frequenties . . . . . . . . . . . . . . . . . . . . . . . . . . 87

8 Bespreking van het volledige systeem 898.1 Inleiding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 898.2 Snelheidsregeling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

9 Lay-out 949.1 Schikking van de onderdelen . . . . . . . . . . . . . . . . . . . . . . . . . . . . 949.2 Verpakking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

10 Handleiding bij de chip 9710.1 Belangrijke opmerkingen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9710.2 Bespreking van de interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9710.3 Correcte instelling van het circuit . . . . . . . . . . . . . . . . . . . . . . . . . 101

10.3.1 Instellen van de digitale logica . . . . . . . . . . . . . . . . . . . . . . 10110.3.2 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10110.3.3 Instellen van de levelshifter . . . . . . . . . . . . . . . . . . . . . . . . 10110.3.4 Instellen van het stroombegrenzingscircuit . . . . . . . . . . . . . . . . 101

10.4 Aanwezige features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

11 Besluit 103

A LV opamps en comparatoren 105A.1 Opamp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

A.1.1 Specificaties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105A.1.2 Ontwerp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106A.1.3 DC-karakteristiek . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107A.1.4 Stabiliteit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

A.2 Comparator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108A.2.1 Ontwerp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108A.2.2 Snelheid . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Inhoudsopgave x

B Gebruikte componenten 111B.1 Componenten uit de bibliotheek van de I3T80 technologie . . . . . . . . . . . 111B.2 Ontworpen logica . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

B.2.1 D-flipflop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113B.2.2 JK-flipflop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

B.3 Modellen voor externe componenten . . . . . . . . . . . . . . . . . . . . . . . 114B.3.1 DC-motor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114B.3.2 Snelheidssensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Bibliografie 118

Lijst van figuren 120

Lijst van tabellen 124

Gebruikte afkortingen

ADC Analoog naar digitaal omzetter

BLN Begraven laag van n-type silicium

BLP Begraven laag van p-type silicium

CMOS Complementary Metal-Oxide-Semiconductor

DC Gelijkstroom

DIP Dual in-line package

DMOS Double-diffused Metal-Oxide-Semiconductor

GND Massapotentiaal

HV Hoogspanning (in dit werk: spanningen hoger dan VCC)

I3T Improved Intelligent Interface Technology

IGBT Insulated Gate Bipolar Transistor

L Transistorlengte

LSB Minst significante bit

LV Laagspanning (in dit werk: spanningen tot VCC)

MOS Metal-Oxide-Semiconductor

NMOS N-kanaals MOSFET

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MSB Meest significante bit

Opamp Operationele versterker

PMOS P-kanaals MOSFET

PWM Pulsbreedtemodulatie

Rpm Toeren per minuut

SOA Veilig werkingsgebied

VCC Laagspanningsvoeding

xi

Hoofdstuk 0. Gebruikte afkortingen xii

VHDL VHSIC Hardware Description Language

VHSIC Very-High-Speed Integrated Circuit

W Transistorbreedte

Hoofdstuk 1

Inleiding

1.1 Kader

In de automobiel-elektronica, robotica en industriele controle worden vaak zogenaamde SmartPower technologieen aangewend. Dit zijn geavanceerde silicium-technologieen waarmee opeenzelfde chip alle vereiste analoge en digitale elektronica kan worden geıntegreerd voor hetrealiseren van een autonoom microsysteem:

Analoge circuits zijn met hun hoge precisie uitermate geschikt voor de signaalcondi-tionering van allerhande sensoren die bv. temperatuur, druk, snelheid of versnellingmeten.

Compacte (maar complexe), snelle digitale logica voor signaalverwerking en lokale in-telligentie.

Speciale schakelingen die werken op hogere spanningen (typisch tot enkele tientallenVolt) en hogere stroomniveaus (typisch tot een paar Ampere) voor het aansturen vanallerlei actuatoren zoals kleine DC-motoren, stappenmotoren, kleppen, . . .

In moderne auto’s zijn tientallen dergelijke microsystemen terug te vinden (figuur 1.1). Denkmaar aan de elektronica voor het activeren van airbags, elektronische ontsteking en brand-stofinjectie, elektronische positionering van de buitenspiegels, . . .

1.2 Probleemstelling

Binnen de TFCG Microsystems onderzoeksgroep gebeurt al vele jaren onderzoek naar hetontwikkelen van nieuwe hoogspanningstransistoren in dergelijke smart power technologieenom met name de performantie van de hoogspannings-uitgangstrappen te verbeteren, en devereiste silicium-oppervlakte te verkleinen. Zo werd onlangs met succes een heel efficiente IG-BT (voluit Insulated Gate Bipolar Transistor) ontwikkeld in de 80 V 0, 35 µm I3T technologie

1

Hoofdstuk 1. Inleiding 2

Figuur 1.1: Smart power technologieen in moderne auto’s

van AMI Semiconductor [1]. Uitvoerige metingen hebben aangetoond dat deze nieuwe com-ponent merkelijk beter presteert dan de reeds bestaande concurrenten (hoogspannings-MOStransistoren), maar tot nu toe werden er met deze IGBT’s nog geen geıntegreerde schakelingenontworpen.

1.3 Doelstelling

In deze thesis wordt voor de eerste maal een volledig monolithisch geıntegreerde elektronischeschakeling rond de nieuwe IGBT’s gebouwd. Hierbij wordt een H-brug ontworpen bestaandeuit 4 IGBT’s, waarmee een kleine DC-motor kan worden aangestuurd. Door gebruik te makenvan PWM-technieken (Pulse Width Modulation) en feedback voor de aansturing van de H-brug, wordt ervoor gezorgd dat de snelheid van de motor in beide richtingen geregeld kanworden onafhankelijk van de belasting.

Het overgrote deel van de tijd wordt gespendeerd aan het ontwerpen van het elektronischschema van de chip en het uitvoeren van alle bijhorende circuit-simulaties. Het te realise-ren elektronisch schema, dat overigens een mooi voorbeeld is van gemengd analoog-digitaalontwerp met een combinatie van laagspannings- en hoogspanningsfuncties, is opgebouwd uitvolgende onderdelen:

De eigenlijke H-brug met de nieuwe IGBT’s die werken op hogere spannings- en stroom-niveaus.

Hoofdstuk 1. Inleiding 3

Niveau-verschuivers (levelshifters) voor het aansturen van de gate-elektrodes van de 2IGBT’s bovenaan in de H-brug.

Een gemengd analoog-digitaal blok dat instaat voor het genereren van de PWM-signalenwaarmee uiteindelijk de gate-elektrodes van de IGBT’s moeten worden geactiveerd. Ditcircuit zal ook zorgen voor snelheidsfeedback.

Een analoog regelcircuit dat op basis van het gemeten stroomniveau in de H-brug, destroom door de IGBT’s beperkt tot een gepaste waarde.

Een thermisch protectiecircuit dat eventuele oververhitting van de IGBT’s voorkomt.

Bij het ontwerp dient in acht genomen te worden dat het volledige systeem op 1 silicium chipmoet komen (monolithisch geıntegreerd), die liefst zo compact mogelijk blijft. Dit zijn dusnog 2 bijkomende, maar niet onbelangrijke specificaties.

Eenmaal het elektronisch schema van de chip volledig is ontworpen, en de simulaties aange-toond hebben dat het circuit naar behoren zou moeten functioneren, wordt overgegaan tothet tekenen van de layout van de chip.

Uiteindelijk zal de chip ook worden gefabriceerd in de 80 V 0, 35 µm I3T technologie van AMISemiconductor. Gelet op de tijd die vereist is voor het vervaardigen van de chip (typisch zo’n3 maanden), gebeurt de evaluatie van de chip buiten het kader van dit afstudeerwerk.

Hoofdstuk 2

Principe van een PWM-gestuurde

H-brug

In dit hoofdstuk wordt een korte inleiding gegeven op de verschillende onderwerpen waarvanhet begrip noodzakelijk is voor het vervolg van dit werk.

2.1 H-brug

Een H-brug (ook wel volle brug genoemd) is een elektrisch circuit dat bestaat uit 4 scha-kelelementen, die typisch in een H-vorm rond een last geschakeld zijn (zie figuur 2.1). Deschakelelementen zijn hierbij vrij te kiezen, en kunnen van het type DMOS, IGBT, . . . zijnnaargelang de specificaties. In wat volgt wordt de werking van een H-brug wat nader bekeken.

(a) H-brug zonder vrijloopdiodes (b) H-brug met vrijloopdiodes

Figuur 2.1: Schematische voorstelling van een H-brug

4

Hoofdstuk 2. Principe van een PWM-gestuurde H-brug 5

2.1.1 Aansturing van een H-brug

Een H-brug kan op verschillende manieren aangestuurd worden. Op basis van de gemiddel-de spanning VOUT die men over de last verkrijgt (of equivalent hiermee: op basis van degemiddelde stroomzin doorheen de last), wordt er een onderscheid gemaakt tussen 2 gevallen.

Unipolaire uitgangsspanning Indien een van de schakelelementen constant actief is, dankomt een van de terminals van de last op een constante spanning (massa of voeding)te staan. Door de andere tak aan te sturen m.b.v. PWM-pulsen, kan de gemiddeldespanning over (en dus ook de gemiddelde stroom doorheen) de last geregeld worden.De gemiddelde spanning over de last kan bij dit type sturing slechts een teken (positiefof negatief) aannemen. Er wordt dus een unipolaire uitgangsspanning verkregen.

Bipolaire uitgangsspanning In dit geval schakelen afwisselend de elementen S1,S4 aanen tegelijk S2,S3 af, of omgekeerd. Beide paren schakelelementen dienen gestuurd teworden door 2 complementaire PWM-pulsen. De gemiddelde spanning over de last kannu zowel negatieve als positieve waarden aannemen. Deze wijze van aansturing geeftdus aanleiding tot een bipolaire uitgangsspanning .

Bij de aansturing van een H-brug dient erop gelet te worden dat 2 schakelelementen uit een-zelfde tak (S1,S2 en S3,S4) nooit simultaan actief zijn. Indien dit wel het geval zou zijn, danzou gedurende die tijd massa met voeding laagohmig verbonden zijn, en dus aanleiding geventot kortsluitstromen. Aangezien dit absoluut vermeden moet worden, bezitten de comple-mentaire stuurpulsen van de H-brug vaak een dode tijd τ . Deze dode tijd hangt uiteraard afvan de gebruikte schakelelementen, de frequentie waarmee geschakeld wordt, . . .

2.1.2 Inductieve last

Indien de eenvoudige H-brug uit figuur 2.1(a) gebruikt wordt om een resistieve last aan testuren, dan zouden er zich geen problemen voordoen. Dit is echter niet het geval bij eeninductieve last zoals een motor. Van een inductieve last is immers geweten dat de stroomdoorheen deze last continu moet zijn. Wanneer een H-brug gebruikt wordt om zo’n last aante sturen, dan moet ervoor gezorgd worden dat de stroom continu kan blijven vloeien. Bijhet eenvoudig schema in figuur 2.1(a) is dit zeker niet het geval gedurende de dode tijd vande stuurpulsen. Zelfs zonder dode tijd kunnen gevaarlijke overgangsverschijnselen optreden.

Om de continuıteit van de laststroom te verzekeren, dienen een aantal vrijloopdiodes in pa-rallel met de schakelelementen geplaatst te worden, en dit zoals voorgesteld in figuur 2.1(b).Door de vrijloopdiodes op deze wijze te schakelen is er altijd een pad aanwezig waarlangsstroom kan vloeien, ook gedurende de dode tijd van de stuurpulsen.

Hoofdstuk 2. Principe van een PWM-gestuurde H-brug 6

Merk tot slot op dat sommige schakelelementen reeds intern een diode kunnen bevatten.Meestal is het echter noodzakelijk om extern over de schakelelementen nog vrijloopdiodes aante brengen.

2.1.3 Aansturen van een motor

Een H-brug wordt vaak gebruikt om snelheid, positie of het koppel van een motor (DC-motor,stappenmotor, . . . ) te regelen. Ook in dit werk staat de snelheidsregeling van een motorcentraal. In wat volgt worden kort wat specificaties opgesomd die voor dit werk gelden.

Het regelen van snelheid en draaizin van een motor komt eigenlijk neer op het regelenvan respectievelijk grootte en stroomzin van de gemiddelde stroom doorheen de motor.Om het regelen van de draaizin van de motor mogelijk te maken, zal de H-brug dusaanleiding moeten kunnen geven tot een bipolaire uitgangsspanning (of dus een gemid-delde laststroom die beide polariteiten kan aannemen). Er is dan ook gekozen voor eendifferentiele aansturing van de diametrale transistorparen van de H-brug.

De elektrische tijdsconstante van de aan te sturen motor bepaalt de benodigde frequentievan de PWM-pulsen. De tijdsconstante van de motor die als referentie gebruikt wordt,bedraagt 1, 2 ms. Meestal wordt de periode van het PWM signaal veel groter gekozendan deze tijdsconstante opdat de stroom door de motor dan min of meer constant blijft.Voor deze motor is een PWM frequentie van 10 kHz dus een goede keuze.

2.2 PWM

PWM (of Pulse Width Modulation) is een techniek waarbij pulsen opgewekt worden waarvanmen de duty-ratio δ kan laten varieren. De duty-ratio δ van een puls wordt hierbij gedefinieerdals de verhouding van de tijd dat de puls hoog is tot de periode van de puls:

δ =ton

T(2.1)

Het opwekken van PWM-pulsen kan op verscheidene manieren gebeuren, en dit zowel analoogals digitaal. In het eenvoudigste geval gaat men uit van een zaagtand- of driehoekssignaal eneen variabel referentieniveau. Door het referentieniveau met het signaal te vergelijken a.d.h.v.een comparator, kan een puls opgewekt worden (zie figuur 2.2(a)). De pulsbreedte van dezepuls kan gevarieerd worden door het referentieniveau te laten varieren. Op deze wijze wordtuiteraard pulsbreedtemodulatie verkregen.

Ook een complementaire puls kan op deze manier makkelijk opgewekt worden. Dit kan bv.gebeuren door de reeds opgewekte puls te inverteren of m.b.v. een tweede comparator waarbij

Hoofdstuk 2. Principe van een PWM-gestuurde H-brug 7

(a) (b)

Figuur 2.2: Genereren van PWM-pulsen

beide ingangen omgewisseld zijn. Er kan ook gebruik gemaakt worden van een tweede referen-tieniveau, zoals bv. voorgesteld in figuur 2.2(b). Deze laatste methode heeft als voordeel datop een eenvoudige manier een dode tijd τ tussen 2 complementaire PWM-pulsen ingevoerdkan worden. Dit is noodzakelijk indien overlap van beide pulsen absoluut vermeden moetworden, zoals het geval is bij de aansturing van een H-brug (zie 2.1 H-brug).

2.3 IGBT’s

(a) Symbool met contacten (A)node,

(K)athode, (G)ate en (B)ulk

(b) Macromodel

Figuur 2.3: De IGBT

In dit werk staan IGBT’s centraal. Zoals reeds vermeld worden ze gebruikt als schakelele-menten in een H-brug.

De werking van een IGBT kan het makkelijkst begrepen worden aan de hand van het eenvoudig

Hoofdstuk 2. Principe van een PWM-gestuurde H-brug 8

macromodel uit figuur 2.3(b). Een positieve spanning op de gate van MOS transistor M1 zalervoor zorgen dat deze gaat geleiden. Dit creeert een basisstroom voor de bipolaire PNPtransistor Q1. Deze basisstroom wordt versterkt door transistor Q1, wat aanleiding geefttot een grote collectorstroom. Transistor Q2 stelt de parasitaire PNP transistor naar hetsubstraat voor.

Een IGBT combineert dus de goede eigenschappen van MOS en bipolaire elektronica. Ener-zijds is er een geısoleerde gate-elektrode, hetgeen eenvoudige spanningssturing toelaat. Ander-zijds wordt een hoge stroomdichtheid bereikt door conductiviteitsmodulatie zoals in bipolairetransistoren. Deze laatste eigenschap laat toe om met compacte componenten toch grotestromen te kunnen voeren.

Hoofdstuk 3

IGBT’s

Een korte inleiding tot IGBT’s werd reeds in 2.3 IGBT’s gegeven. In wat volgt worden destructuur en eigenschappen van deze componenten wat nader bekeken.

3.1 IGBT’s in de I3T80 technologie van AMIS

Tot dusver konden IGBT’s nog niet concurreren met de reeds bestaande HV MOS-transistorenvoor het gebruik in bijvoorbeeld de automobielelektronica. IGBT’s moeten namelijk competi-tie aangaan met de goed ingeburgerde DMOS transistoren. Bovendien is een integratie samenmet CMOS logica moeilijk door de grote substraatstroom en overspraak die deze hoogspan-ningscomponenten veroorzaken. Binnen de TFCG Microsystems onderzoeksgroep heeft meneen heel efficiente IGBT ontwikkeld die deze concurrentie mogelijks wel aankan [2, 3, 4]. DezeIGBT werd ontworpen in de 80V 0, 35 µm I3T80 technologie van AMI Semiconductor. Hier-onder wordt deze component vergeleken met een reeds bestaand ontwerp. De getekende lagenuit de I3T80 technologie zijn beschreven in [5]. In [1] wordt de technologie voorgesteld.

3.1.1 Klassieke n-LIGBT structuur

In figuur 3.1 is een structuur te zien van een n-type laterale IGBT zoals deze klassiek gekendis [6]. In aangeschakelde toestand ontstaat in het n-epi gebied tussen kathode en anodeeen plasma van elektronen (afkomstig van de kathode) en gaten (afkomstig van de anode),d.i. een extreem hoge concentratie aan vrije ladingsdragers. Dit is het fenomeen gekend alsconductiviteitsmodulatie, hetgeen optreedt in bipolaire componenten en zorgt voor een hogestroomdichtheid.

Deze eenvoudige IGBT structuur heeft echter enkele nadelen. Eerst en vooral is deze IGBTgevoelig aan latch-up. Tussen anode en kathode is namelijk een parasitaire PNPN thyristoraanwezig. Indien die aanschakelt is de stroom doorheen de IGBT niet meer bepaald door demate dat de gate aangestuurd wordt, maar zal deze stroom sterk toenemen. Dit is bijna altijd

9

Hoofdstuk 3. IGBT’s 10

Figuur 3.1: Structuur van een klassieke IGBT

destructief. Het gebied dat gevoelig is voor deze latch-up bevindt zich onder het gate-oxidein de buurt van de n+-p-well junctie. In principe is deze junctie kortgesloten want kathodeen bulk zijn met elkaar verbonden. Aangezien de p-well echter niet zwaar gedopeerd is,bevat deze een bepaalde weerstand waarover een spanningsval kan bestaan. Bij een bepaaldeanodestroom zal deze spanningsval groot genoeg worden, waardoor de PNPN thyristor zalontsteken en er latch-up optreedt. Bij deze klassieke structuur treedt latch-up op bij relatieflage waarden van de anodestroom.

Een tweede probleem is de substraatstroom injectie. Tussen anode en substraat is er een para-sistaire PNP transistor aanwezig. Zelfs bij normale werking zal deze transistor aangeschakeldzijn (zie figuur 2.3(b)). Daardoor is er injectie van gaten in het substraat wat leidt tot sub-straatstromen. Op het eerste zicht is dit geen probleem aangezien de goede werking van decomponent niet in gevaar lijkt te komen. De stroom kan inderdaad niet onbeperkt toenemen,maar wordt gestuurd door de basisstroom van de (slechte) parasitaire bipolaire transistor.Nu is het echter zo dat een IGBT in een microsysteem meestal niet als aparte componentop een chip staat en het blijkt dat substraatstromen kunnen leiden tot allerlei ongewensteparasitaire effecten. Het is dus zeker belangrijk om deze substraatstromen te vermijden.

Hoofdstuk 3. IGBT’s 11

3.1.2 Verbeterde n-LIGBT structuur

Dit nieuwe ontwerp probeert een oplossing te zoeken voor de twee belangrijkste gebrekenvan de klassieke structuur, namelijk latch-up en substraatstromen. Hiertoe is een doubleburried layer structure gebruikt. De structuur van deze IGBT is schematisch weergegeven infiguur 3.2. Voor een gedetailleerde bespreking wordt verwezen naar [2, 3, 4]. In deze paragraafworden enkele aspecten behandeld die belangrijk zijn voor het circuit dat beschreven is in ditwerk.

Figuur 3.2: Structuur van de nieuw ontwikkelde IGBT

Door de extra BLP laag worden de anode en het substraat van elkaar geısoleerd. Daardoor iser geen parasitaire bipolaire transistor meer naar het substraat, waardoor ook de substraat-stroom vele grootteordes naar omlaag gehaald is en zo verwaarloosbaar wordt (figuur 3.3).Het probleem van de latch-up wordt aangepakt door de BLP te combineren met een zwaarge-dopeerd p-sinker gebied onder de kathode. Dit p-gebied dat fungeert als burried hole diverterleidt de gatenstroom af van het oppervlak van de component, dit is namelijk het gebied datgevoelig is voor latch-up.

Deze structuur heeft nog enkele andere voordelen waarvan de belangrijkste hieronder wordenopgesomd [3, 4].

De verhouding van de substraatstroom tot anodestroom is 4 a 5 grootteordes lager ten

Hoofdstuk 3. IGBT’s 12

Figuur 3.3: Vergelijking van de substraatstroom bij de klassieke IGBT structuur en het verbeterdeontwerp met een “double burried layer” [3]

opzichte van die bij de klassieke IGBT structuur (figuur 3.3) .

Het schakelen van de IGBT gebeurt sneller.

Er is een grote “safe operating area” voor de IGBT doordat latch-up pas optreedt bijgrotere anode-kathodespanning en hogere anodestroom.

De BLN laag zorgt ervoor dat de IGBT zwevend is, waardoor deze n-type IGBT perfectkan geıntegreerd worden in een uitgangstrap of H-brug als “high side switch”).

Er zijn maar weinig vermogensverliezen wanneer de IGBT geleidt en schakelt.

De IGBT kan in een bestaande Smart Power technologie gemaakt worden zonder hettoevoegen van extra maskers.

In vergelijking met klassieke DMOS transistoren is er een hoger stroomniveau per op-pervlakte silicium bij grote stromen (figuur 3.4).

Helaas zijn er ook enkele nadelen aan deze component verbonden.

Over de component in geleiding staat minstens een vaste spanningsval van een drempel≈ 0, 6 V.

Hoofdstuk 3. IGBT’s 13

Latch-up kan nog steeds optreden, hoewel slechts bij hoge waarden van VAK en IA.

Figuur 3.4: Vergelijking van de stroomdichtheid bij de verbeterde IGBT en bij een DMOS transistor

Aan de hand van simulaties kan de hogere stroomdichtheid van een IGBT inderdaad bevestigdworden. De uitgangskarakteristiek van een laterale n-type DMOS (lfndm14 ) met dezelfdestroomvoerende oppervlakte werd vergeleken met deze van de gebruikte IGBT. Op basis vandeze oppervlakte werden volgende afmetingen gekozen:

DMOS (lfndm14 ):W = 2200µm (18 vingers) (3.1)

IGBT:W = 960µm (8 vingers) (3.2)

Op figuur 3.6 is het resultaat weergegeven. Eerst en vooral is de saturatiestroom (bij hogeVDS of VAK) bij de IGBT veel groter. Bij gebruik in de H-brug is het lineaire werkings-gebied echter het interessantst. Voor zeer lage stromen lijkt een DMOS het best aangeziende spanningsval over de component het kleinst is. Hierdoor zal de dissipatie dus ook lagerzijn. De reden hiervoor is de aanwezigheid van de bipolaire structuur in de IGBT. Daar-door zal over de IGBT steeds een drempelspanning staan. Naarmate de stroom toeneemt,presteert de IGBT steeds beter. De lagere aan-weerstand van de IGBT is hiervan de oor-zaak waardoor vanaf een bepaald stroomniveau een IGBT interessanter wordt. Ook moet

Hoofdstuk 3. IGBT’s 14

vermeld worden dat geen volledig equivalente component werd gevonden in de bibliotheekvan de I3T80 technologie om de IGBT mee te vergelijken. De lfndm14 kan eigenlijk maar tot14 V gebruikt worden, waardoor die compacter kan gemaakt worden. Daardoor werden deprestaties (stroom per oppervlakte-eenheid) van de DMOS in deze simulatie overschat en isde IGBT dus beter dan zou blijken uit deze resultaten. Dit is ook op te maken uit de groteverschillen in transistorbreedtes in (3.1) en (3.2), voor een zelfde oppervlakte silicium.

3.2 Elektrische karakteristieken van de IGBT

Figuur 3.5: Het gebruikte macromodel: M1 is een lfndm14 transistor met W = 40 × 78 µm; Q1 iseen vphb5u0 met oppervlakte = 117× 25 µm2

De gebruikte IGBT’s zijn nog niet zo lang geleden ontworpen en zijn dus nog niet beschikbaarals component in de bibliotheek van de I3T80 technologie. Een bijhorend elektrisch (SPICE)model is dus ook nog niet voorhanden. De IGBT’s zijn echter uitvoerig getest en opgemetendoor de onderzoeksgroep. Aan de hand daarvan werd een eenvoudig macromodel (figuur 3.5)opgesteld waarop het ontwerp van deze chip gebaseerd is. Hoewel het model eenvoudig is,blijkt het toch goed overeen te komen met de realiteit. De bespreking hieronder baseert zichdan ook op dit macromodel. Hoewel er dus kleine afwijkingen kunnen zijn met de werkelijkekarakteristieken, is het vooral de bedoeling om inzicht te verwerven in de werking van decomponent met het oog op het ontwerp van de levelshifter.

3.2.1 De IGBT in DC

De uitgangskarakteristiek horende bij het macromodel is getoond in figuur 3.6, samen metde karakteristiek van een vergelijkbare DMOS. Zoals reeds besproken, heeft de IGBT eenkleinere aan-weerstand Ron dan een DMOS, maar wel een vaste spanningsval van een drempel≈ 0, 6 V. Uit de figuur blijkt dat de gebruikte IGBT’s gedimensioneerd zijn voor een maximalesaturatiestroom van 1, 5 A. Uiteraard moet de stroom in een IGBT die als schakelaar gebruikt

Hoofdstuk 3. IGBT’s 15

wordt, een stuk lager blijven dan deze saturatiestroom. Er is gekozen om de stroom door deIGBT’s te beperken tot 0, 5 A (zie Hoofdstuk 6 De H-brug met protectiecircuits). Uit figuur 3.6blijkt dat de IGBT in dat geval nog steeds in zijn lineair gebied werkt en de spanningsvalerover nog aanvaardbaar is, hetgeen gewenst is.

Figuur 3.6: Vergelijking van de stroomdichtheid bij de IGBT (IA) en bij een DMOS (ID) doorhet uitvoeren van een simulatie met componenten die evenveel siliciumruimte in beslagnemen. Voor de IGBT werd het macromodel uit figuur 3.5 gebruikt.

Hoofdstuk 3. IGBT’s 16

3.2.2 Safe Operating Area

Figuur 3.7: Vereenvoudigde Safe Operating Area karakteristiek van de IGBT: toegelaten en verbodenzones in de uitgangskarakteristiek.

Om doorslag van het dunne gate-oxide te vermijden, moet de gate-kathodespanning VGK

zeker lager blijven dan 3, 6 V (liefst zelfs 3, 3 V). De doorslagspanning van een afgeschakeldecomponent is 75 V. De anode-kathodespanning VAK mag tot 47 V bedragen in aangeschakeldetoestand. Voorzichtigheid is echter geboden bij gelijktijdig grote VAK en IA. In dat gevalkan latch-up optreden, hoewel deze verbeterde IGBT op dit vlak veel beter presteert dan eenklassieke structuur. Op figuur 3.7 is grafisch en vereenvoudigd weergegeven welke het veiligewerkingsgebied is voor de IGBT. Dit noemt met de Safe Operating Area van een component.

3.2.3 Schakelgedrag van een igbt

Om het gedrag van 1 IGBT te onderzoeken baseert men zich vaak op de schakeling uitfiguur 3.8. De transistor wordt nooit rechtstreeks aangestuurd door een spanningsbron. Sig-nalen afkomstig van het (digitale) stuurcircuit worden na buffering of door middel van eenlevelshifter aangelegd tussen gate en kathode van de IGBT om op die manier de componentaan of af te schakelen. Dit heeft tot gevolg dat de IGBT niet ogenblikkelijk aangeschakeldwordt. In het geval van figuur 3.8 kunnen de twee invertoren (buffers) vervangen wordendoor een equivalente serieweerstand, hetgeen leidt tot een soort RC-gedrag. Het aanschake-len van de transistor is weergegeven in figuur 3.9(a). In deze figuur kunnen een aantal fasenonderscheiden worden [7, 8].

Hoofdstuk 3. IGBT’s 17

Figuur 3.8: Opstelling om het schakelgedrag van de IGBT te onderzoeken (VHV = 25V)

(1) In het eerste interval stijgt de gate-kathodespanning VGK van 0 tot de drempelspanningVT . Dit leidt tot een tijdvertraging bij het aanschakelen. De anodestroom IA en deanode-kathodespanning VAK of Vout blijven ondertussen constant.

(2) Vervolgens bereikt VGK de waarde VT en begint de IGBT te geleiden. IA begint toe tenemen.

(3) Gedurende de derde periode treedt een Miller plateau op. De stroom in de gatecapaci-teit, IG, is min of meer constant en het lijkt dus alsof deze capaciteit oneindig is. Vout

begint snel te dalen waardoor de parasitaire Millercapaciteit CGA (tussen gate en ano-de) ontladen moet worden. Een groot deel van de stroom in de gate wordt gebruikt omdeze capaciteit CGA te ontladen. Door de parasitaire junctiecapaciteit van de diode D

is er een piek te zien in de anodestroom IA en op het Miller plateau uit de golfvorm vanVGK . Deze pieken komen inderdaad overeen met de inverse stroom ID door de diode.Dit fenomeen is gekend als reverse recovery . Bij gebruik van een ideale diode, zou degolfvorm van IA een monotoon verloop kennen en zou het Miller plateau in VGK vlakzijn.

(4) VGK neemt exponentieel toe naar de eindwaarde. IG neemt exponentieel af.

Het gesimuleerde gedrag bij het aanschakelen van de gebruikte IGBT komt in grote lijnenovereen met besprekingen uit de literatuur [7, 8]. Doordat de simulaties uitgevoerd werdenmet een macromodel, kan het wel zijn dat er lichte afwijkingen optreden ten opzichte vande werkelijkheid. Dit is echter niet zo belangrijk voor het ontwerp van de levelshifter enaanstuurelektronica van de ontworpen chip.

In figuur 3.9(b) is het gesimuleerde afschakelen van de IGBT getoond. Hierbij moet vermeldworden dat de simulaties met het macromodel enigszins afwijken van de realiteit. In deliteratuur vindt men een licht andere vorm van de golfvormen [7, 8].

Hoofdstuk 3. IGBT’s 18

(a) Aanschakelen (b) Afschakelen

Figuur 3.9: Simulatieresultaten van de opstelling uit figuur 3.8 met het macromodel voor de IGBTuit figuur 3.5.

(1) De gatespanning VGK begint af te nemen en IA en Vout blijven min of meer constant.

(2) VGK bereikt de waarde waarbij het Miller plateau optreedt en blijft gedurende dezeperiode constant. Vout begint toe te nemen. In tegenstelling tot de simulatie met hetmacromodel, zal Vout in realiteit gedurende deze fase quasi de eindwaarde bereiken.Daarom noemt met dit ook de voltage rise phase van het afschakelen.

(3) IA daalt snel en ook VGK neemt verder af. Aangezien de stroom door de spoel L continumoet zijn, begint de vrijloopdiode D te geleiden.

(4) Wanneer VGK lager wordt dan VT schakelt de MOS transistor, die deel uitmaakt van hetingangsgedeelte van de IGBT, af. IA neemt verder af met een staartstroom. Dit is hetgevolg van recombinatie van minoritaire ladingsdragers in het substraat. Het is duidelijkdat deze staartstroom verantwoordelijk is voor een groot deel van de schakelverliezen.

Zoals reeds vermeld wijkt deze simulatie af van het betere schakelgedrag in de realiteit. Hetafschakelen van de gebruikte IGBT werd reeds opgemeten [4] en is weergegeven in figuur 3.10.Tijdens de “voltage rise phase” stijgt Vout en blijft de stroom constant. In de fase (3) daarnadaalt de stroom bijna ogenblikkelijk en is er geen staartstroom zoals men zou verwachten bij

Hoofdstuk 3. IGBT’s 19

Figuur 3.10: Opgemeten golfvorm van de anodestroom in de IGBT bij het afschakelen (opstelling uitfiguur 3.8 met L = 2, 35 mH en VHV = 50 V). De gate wordt gedurende 500 ns vollediggeopend en vervolgens afgeschakeld. Na de voltage rise phase daalt de anodestroombijna ogenblikkelijk naar 0. De invloed van de uitgangscapaciteit bij het afschakelen isook getoond [4].

IGBT’s. Dit is te danken aan de aanwezigheid van de p-sinker en BLP. Voor meer informatiehieromtrent wordt verwezen naar [4].

Hoofdstuk 4

Generatie van PWM-pulsen

4.1 Inleiding

In dit werk is ervoor gekozen om de PWM-pulsen op een digitale [9] wijze te genereren.Op deze manier wordt het ontwerp van een schakeling met analoge componenten vermeden,wat uiteraard tijdrovender en kritischer is. Een digitale realisatie neemt ook zeer weinigsiliciumruimte in beslag. In dit hoofdstuk wordt de digitale opwekking van PWM-pulsen watnader bekeken.

4.2 Principe

Voor de sturing van een H-brug zijn 2 complementaire PWM-pulsen nodig (zie 2.1.1 Aanstu-ring van een H-brug). Zoals reeds in vorige paragraaf vermeld, worden de PWM-pulsen indeze thesis op een digitale wijze gegenereerd. Hiertoe wordt vertrokken van een eenvoudigemaar synchrone teller.

Beschouw een synchrone teller die voortdurend van begin- tot eindwaarde telt. Dit kan als hetware gezien worden als een digitaal zaagtandsignaal. Het synchrone karakter van de teller ishierbij noodzakelijk om van een mooi zaagtandsignaal te kunnen spreken. Bij een asynchroneteller zou het signaal immers niet-gewenste overgangsverschijnselen vertonen.

Omdat een dode tijd tussen de 2 pulsen nodig is om kortsluitstromen in de H-brug te ver-mijden, zal een zaagtandsignaal hier niet volstaan. Een dode tijd τ is, zoals reeds eerdervermeld, veel makkelijker te realiseren indien gebruik gemaakt wordt van een driehoekssig-naal en 2 referentieniveaus die een zekere waarde ∆ van elkaar verschillen. De teller die alsstartpunt beschouwd werd dient dus zo gemodificeerd te worden dat deze achtereenvolgensop- en aftelt. Op deze wijze wordt een digitaal driehoekssignaal verkregen (zie ook figuur 4.1).

Eenmaal het driehoekssignaal beschikbaar is, wordt m.b.v. een logisch circuit (op te vatten

20

Hoofdstuk 4. Generatie van PWM-pulsen 21

als een digitale uitvoering van een comparator) het verschil bepaald tussen dit signaal SIG

en beide variabele referentieniveaus NIV1 en NIV2. Door dit op een gepaste manier te doen,rekening houdend met de ‘polariteit’ van de ingangen van de digitale comparator, zullen deborrow-bits gegenereerd door beide logische circuits de gewenste PWM-pulsen opleveren. Ditis schematisch voorgesteld in figuur 4.1

Figuur 4.1: Opwekken van 2 complementaire PWM-pulsen a.d.h.v. een digitaal driehoekssignaal

4.3 Realisatie van de verschillende bouwblokken

Het principe van de generatie zoals hierboven uitgelegd is vrij eenvoudig. In deze paragraafwordt de realisatie van de verschillende bouwblokken wat toegelicht.

4.3.1 Gemodificeerde teller

Om een nauwkeurige resolutie te bekomen wordt een synchrone 9-bit teller gebruikt voor degeneratie van de PWM-pulsen. Met 9 bits is de gemiddelde stroom doorheen de last vande H-brug (en in dit geval dus ook de snelheid van de motor) in principe te regelen in 29

(=512) verschillende niveaus. Het synchrone karakter is zoals reeds vermeld nodig om eenmooi zaagtandsignaal zonder overgangsverschijnselen te verkrijgen.

Voor de teller wordt vertrokken van een klassieke uitvoering waarbij 9 flipflops in serie gescha-keld worden (aangeduid door stippellijn op figuur 4.2). Uiteraard dient, om een synchroonkarakter te garanderen, elk van deze flipflops door een en dezelfde klok gestuurd te worden.Voor de flipflops wordt dan ook het type JK-flipflop gekozen.

De opbouw van de teller is zeer eenvoudig. Beide ingangen van de eerste JK-flipflop worden

Hoofdstuk 4. Generatie van PWM-pulsen 22

aan voeding (= logische “1”) gehangen zodat de uitgang elke dalende klokflank van waardeverandert. Deze uitgang wordt de minst beduidende bit van de teller. De ingangen van dedaaropvolgende flipflops worden vervolgens met de uitgang van de voorgaande verbonden.Voor een correcte werking dienen nog een aantal logische AND-poorten ingevoerd te worden.Deze zorgen ervoor dat de uitgang van elke volgende flipflop slechts van waarde verandert alsde voorgaande allemaal een logische “1” aan de uitgang hebben. Op deze wijze voert elk vande flipflops als het ware een frequentiedeling uit, wat duidelijk op een teller-werking duidt.

Om nu een digitaal driehoekssignaal te genereren, wordt na de laatste (9de) flipflop nog eenflipflop geschakeld. Deze zal aan zijn uitgang een logische “1” creeren wanneer de tellerzijn eindwaarde bereikt. Dit signaal kan beschouwd worden als een controlesignaal dat aan-geeft wanneer het geheel moet beginnen aftellen. Dit kan vrij eenvoudig gerealiseerd wordendoor elk van de 9 uitgangsbits van de teller samen met dit controlesignaal door een logischeXOR-poort te sturen (zie figuur 4.2; merk op dat het controlesignaal best gebufferd dientte worden). Op deze manier blijven de uitgangsbits van de teller ongewijzigd wanneer hetcontrolesignaal een logische “0” is (teller telt op), maar klappen alle uitgangsbits om wanneerhet controlesignaal een logische “1” aanneemt (teller telt af).

Een simulatie van deze gemodificeerde teller wees uit dat de 9 uitgangssignalen een dipjevertonen bij de overgang van optellen naar aftellen. Dit dipje treedt op doordat de flankenvan de ingangssignalen aan de logische XOR-poorten overlappen. Aangezien dit aanleidingzou kunnen geven tot gedeeltelijke overlap van de flanken van beide PWM-pulsen, en dus toteen gelijktijdige geleiding (zij het van heel korte duur) van 2 IGBT’s in eenzelfde tak van deH-brug, moet hier zeker een extra voorzorg genomen worden. Een oplossing hiervoor wordtbesproken in 4.4 Globaal schema.

4.3.2 Klok ter aansturing van de gemodificeerde teller

Voor de PWM-pulsen, en dus ook voor het bijhorende driehoekssignaal, is een frequentie vanongeveer 10 kHz gewenst (zie 2.1.3 Aansturen van een motor). Aangezien de teller als hetware 10 frequentiedelingen uitvoert, dient deze dus aangestuurd te worden door een klok meteen frequentie van 10, 24 MHz.

Figuur 4.2: Gemodificeerde teller

Hoofdstuk 4. Generatie van PWM-pulsen 23

Kwalitatieve bespreking

Voor de klok zijn er een aantal mogelijke oscillatoren weergegeven in figuur 4.3. Niet elk vandeze types blijkt hier echter mogelijk.

(a) (b)

(c) (d)

Figuur 4.3: Enkele oscillator-topologieen

(a) Bij oscillatoren van dit type wordt de spanning aan de ingang van een logisch poortje(in dit geval een invertor) tijdelijk hoger dan de voedingsspanning van 3, 3 V. Aangeziendit absoluut moet vermeden worden, is een klok gebaseerd op dit type oscillator (en alzijn varianten) zeker uit te sluiten.

(b) Ringoscillatoren komen vaak voor on-chip. De frequentie van dit soort oscillatoren hangtechter af van de delay van elk logisch poortje. Het spreekt voor zich dat het gebruik vaneen ringoscillator vrij gevoelig is voor variaties op de delay van elk poortje en daardoorerg onnauwkeurig kan zijn.

(c) Bij dit type wordt gebruik gemaakt van een versterker. Aangezien een klokfrequentievan 10, 24 MHz gewenst is, lijkt ook dit type niet mogelijk. Dit circuit zou immers eenveel te grote bandbreedte van de versterker vergen.

(d) Dit type oscillator is eigenlijk een algemeen geval van vorig type; de Schmitt-Triggerwordt niet noodzakelijk m.b.v. een versterker uitgevoerd. De frequentie van de oscillatorkan van een groot aantal factoren (R, C, VCC , VSat, VT , . . . ) afhankelijk zijn. Dit isnatuurlijk ten nadele van de precisie van de klokfrequentie.

Hoofdstuk 4. Generatie van PWM-pulsen 24

Uit voorgaande bespreking volgt dat een uitvoering van het type (d) de beste keuze lijkt.Voor de Schmitt-Trigger dient echter wel een realisatie zonder versterkers gebruikt te worden.

Schmitt-Trigger

De gerealiseerde uitvoering van een Schmitt-Trigger in CMOS-technologie is te zien in fi-guur 4.4. Het werkingsprincipe wordt kort besproken in wat hierop volgt.

Figuur 4.4: Schmitt-Trigger in CMOS-technologie

Wanneer VIn gelijk is aan 0V, dan geleiden de transistoren M4 en M5. VOut neemt de waardevan de voedingsspanning VCC aan. Transistor M3, die als source-volger geschakeld is, zalovergaan tot geleiding. De source van M2 komt hierdoor op een spanning VCC −VT te staan.Indien VIn stijgt tot een drempelspanning VT , dan zal M1 beginnen geleiden. M1 en M3 diezich beiden in geleidingstoestand bevinden, vormen samen een spanningsdeler. De source vanM2 komt dus op een spanning VCC

2 te staan. Indien VIn verder stijgt tot VCC2 + VT , dan zal

ook M2 stilaan tot geleiding overgaan, en VOut zal dalen. Bijgevolg dalen ook de gatespanningvan de source-volger M3 en de sourcespanning van M2. Eveneens doordat de spanning VOut

daalt, begint M6 (source-volger) te geleiden en M4 schakelt helemaal af. Ook M5 schakeltaf wanneer VIn nog verder stijgt. Een gelijkaardige redenering kan gemaakt worden wanneerVIn terug laag gebracht wordt.

Dimensionering

Het kan makkelijk geverifieerd worden dat voor Oscillator (d), de frequentie van het uitgangs-signaal gegeven wordt door de algemene formule (4.1).

Hoofdstuk 4. Generatie van PWM-pulsen 25

f =1

RC ln[(

V2−V −sat

V1−V −sat

)(V1−V +

sat

V2−V +sat

)] (4.1)

Hierbij stellen V1 en V2 in (4.1) respectievelijk het laagste en hoogste kippunt van de Schmitt-Trigger voor, terwijl V −

sat en V +sat respectievelijk de lage en hoge saturatiespanning van de

Schmitt-Trigger voorstellen.

De uitgang van de Schmitt-Trigger schakelt in het ideale geval tussen 0V en VCC . Invullenvan deze waarden voor V −

sat en V +sat in de algemene formule (4.1) leidt tot (4.2).

f =1

RC ln[(

V2V1

)(V1−VCCV2−VCC

)] (4.2)

De frequentie van de klok blijkt dus afhankelijk te zijn van de kippunten, de voedingsspanningen de tijdsconstante RC.

De theoretische waarden voor de kippunten werden reeds bepaald bij de bespreking van deSchmitt-Trigger als zijnde V1 = VCC

2 − VT en V2 = VCC2 + VT . Uitvoeren van een simulatie,

dat met zijn nauwkeurigere modellen een betere schatting geeft, levert uiteindelijk volgendewaarden voor de kippunten: V1 = 1, 17 V en V2 = 2, 02 V. Eenmaal deze waarden gekend,rest er enkel nog een RC-circuit dat gedimensioneerd moet worden. Hierbij wordt in achtgenomen dat de oppervlaktes van de weerstand en capaciteit ongeveer even groot moeten zijnom tot een minimaal oppervlaktegebruik in de layout te komen. Dit kan makkelijk nagegaanworden door een extremumonderzoek uit te voeren op de oppervlakte-functie (4.3), waarinW de breedte van een ’square’ voorstelt van de weerstand R.

A(R,C)[µm2] =R

1 kΩW 2[µm2] +

C

1, 5 fF/µm2(4.3)

Bovenstaande opmerking en vergelijking (4.2) leveren dus een eerste schatting voor R en C.Het uitvoeren van enkele simulaties levert uiteindelijk de definitieve waarden (4.4). Bij hetbepalen van deze definitieve waarden wordt er op simulaties gesteund omdat de modellen diein Cadence zijn opgenomen, nauwkeuriger zijn.R = 100 kΩ

C = 0, 74 pF(4.4)

De gedimensioneerde versie van de klok is afgebeeld in figuur 4.5. Bemerk de aanwezigheidvan een buffer aan de uitgang om de klokflanken steiler te maken.

Hoofdstuk 4. Generatie van PWM-pulsen 26

Figuur 4.5: Gedimensioneerde versie van de klok

Externe oscillator

Naast de aanwezigheid van een interne oscillator, is er ook de mogelijkheid voorzien om externeen oscillator aan te leggen. De interne oscillator genereert immers een uitgangssignaal meteen vaste frequentie van 10, 24 MHz, en legt dus meteen ook de frequentie van de PWM-pulsen vast op 10 kHz. Het is dus zeker interessant om ook het aanleggen van een externeoscillator mogelijk te maken om bv. het schakelgedrag van de IGBT’s bij hogere frequenties tekunnen bestuderen. Bovendien is de gewenste PWM frequentie afhankelijk van de gebruikteDC-motor.

Om de keuze intern/extern kloksignaal mogelijk te maken, wordt een extra logisch circuittoegevoegd dat de keuze maakt a.d.h.v. een keuzebit. Indien het keuzebit de logische waarde“0” (“1”) aanneemt, dan wordt het intern (extern) kloksignaal geselecteerd. De waarheidsta-bel die hiermee overeenstemt is weergegeven in tabel 4.1; karnaughkaart en corresponderendminimaal logisch circuit in figuur 4.6 [9].

Intern Extern Keuze Out

0 0 0 00 0 1 00 1 0 00 1 1 11 0 0 11 0 1 01 1 0 11 1 1 1

Tabel 4.1: Keuze intern/extern kloksignaal: waarheidstabel

Hoofdstuk 4. Generatie van PWM-pulsen 27

(a) Karnaughkaart (b) Logisch circuit

Figuur 4.6: Keuze intern/extern kloksignaal: karnaughkaart (a) en logisch circuit (b)

4.3.3 Sommatie-circuit

Het sommatie-circuit dat een tweede niveau uit het opgegeven referentieniveau afleidt door ereen waarde ∆ bij op te tellen, bestaat in zijn meest algemene vorm uit een aaneenschakelingvan full-adders. Echter, naargelang de waarde die voor ∆ (zie figuur 4.1) gekozen wordt,zullen nog enkele vereenvoudigingen doorgevoerd kunnen worden.

Zoals uit 4.4 Globaal schema zal blijken, wordt voor ∆ een waarde 15 (binair: 1111) gekozen.In het vereenvoudigd sommatie-circuit zullen dus 4 full-adders noodzakelijk zijn, gevolgd dooreen logisch circuit dat enkel nog rekening houdt met het carry-bit van de laatste full-adder.Het resulterend sommatie-circuit is voorgesteld in figuur 4.7.

Figuur 4.7: Vereenvoudigd sommatie-circuit (∆=15)

4.3.4 Comparator

Het afleiden van een puls uit referentieniveau en driehoekssignaal kan eenvoudig gebeurena.d.h.v. een logisch circuit dat het teken (d.i. het borrow-bit) van het verschil tussen beidebepaalt. Hiertoe wordt vertrokken van een waarheidstabel voor het verschil tussen 2 bits

Hoofdstuk 4. Generatie van PWM-pulsen 28

X en Y (tabel 4.2). Vervolgens wordt m.b.v. een karnaughkaart (figuur 4.8(a)) volgendecorresponderende minimale Boolese vorm afgeleid: BOut = XBIn+(X+Y )BIn. Het minimalelogisch circuit dat met deze Boolese vorm overeenstemt (figuur 4.8(b)) wordt vervolgens 9 keerin serie geschakeld om tot de gewenste digitale comparator te komen.

X Y BIn D BOut

0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 0 11 0 0 1 01 0 1 0 01 1 0 0 01 1 1 1 1

Tabel 4.2: Verschil tussen 2 bits X en Y: waarheidstabel

(a) Karnaughkaart (b) Logisch circuit

Figuur 4.8: Verschil tussen 2 bits X en Y: karnaughkaart (a) en logisch circuit (b)

4.4 Globaal schema

De verschillende circuits die in vorige sectie beschreven staan, dienen tot slot gecombineerdte worden om zo de gewenste PWM-pulsen op te wekken. Dit is schematisch voorgesteld infiguur 4.9(a).

Onder 4.3.1 Gemodificeerde teller is reeds vermeld dat er nog een extra voorzorg genomenmoet worden om het probleem van de dipjes in de uitgangssignalen van de gemodificeerdeteller op te lossen (en om eigenlijk glitches waar dan ook in het digitale systeem te elimi-neren). Dit kan eenvoudig gebeuren door na beide comparators in figuur 4.9(a) nog eenD-flipflop te schakelen (zie figuur 4.9(b)), en deze aan te sturen met het kloksignaal zodat het

Hoofdstuk 4. Generatie van PWM-pulsen 29

(a) Principeschema

(b) Aangepast schema

Figuur 4.9: Globaal schema: opwekken PWM-pulsen

volledige systeem synchroon werkt. Op die manier worden de signalen aan de uitgang vande comparators (die dipjes kunnen bevatten) doorgegeven aan de uitgang van de D-flipflopgedurende de dalende flank van de klok. Aangezien gedurende de dalende klokflank de dipjesreeds uitgestorven zijn, zal dit aanleiding geven tot bruikbare PWM-pulsen zonder overlapvan flanken.

Zoals reeds eerder vermeld, dient tussen beide PWM-pulsen een zekere dode tijd τ te wordenvoorzien. Hiertoe wordt een gepaste waarde voor ∆ gekozen, d.i. het verschil tussen beidereferentieniveaus (zie ook figuur 4.1). Het verband tussen ∆ en de dode tijd τ wordt hierbijgegeven door (4.5). Merk op dat de uitgang van de comparator (borrow-bit) reeds laag wordtals beide ingangen gelijk zijn, vandaar de factor ∆ + 1.

Hoofdstuk 4. Generatie van PWM-pulsen 30

τ =( 1

10, 24 MHz

)(∆ + 1) (4.5)

Uit simulaties van de H-brug met de levelshifters en IGBT’s als schakel-elementen, blijkt datdeze in een tijd van ongeveer 100 ns ontladen zijn. Aldus zal voor de gerealiseerde H-brug opzijn minst een dode tijd τ = 100 ns noodzakelijk zijn. Om hier toch enige marge in te bouwen,wordt ∆ = 15 gekozen. Dit stemt overeen met een dode tijd τ = 1, 56 µs indien de interneklok gebruikt wordt. Bovendien is deze dode tijd afhankelijk van de klokfrequentie. De dodetijd wordt groter gekozen dan strikt noodzakelijk opdat het circuit ook nog zou werken bijtesten met eventuele hogere klokfrequenties.

Een laatste punt waar rekening mee gehouden moet worden, is dat voor beide pulsen een zekereminimale pulsbreedte noodzakelijk is. De noodzaak hiervan zal blijken uit de beschrijving vande gebruikte levelshifter (zie 5.2 Principeschema). Omdat de realisatie van deze minimalepulsbreedte het makkelijkst te implementeren is in combinatie met de snelheidsregeling, wordtdit besproken in 7.3.1 Minimale pulsduur PWM1 en PWM2.

4.5 Resultaten

Ter volledigheid wordt nog een simulatie van de PWM-pulsen opgenomen. In figuur 4.10zijn de PWM-pulsen voor en na de D-flipflop van figuur 4.9(b) opgenomen, respectievelijkvoorgesteld door PWM ′ en PWM . De glitches in PWM ′ waarvan sprake in 4.4 Globaalschema zijn duidelijk op te merken. Verder kunnen periode en dode tijd afgelezen worden oprespectievelijk figuur 4.10(a) en figuur 4.10(b). Deze blijken zeer goed te beantwoorden aande verwachte waarden.

4.6 Werking bij hogere frequenties

Handig om weten is een bovengrens voor de frequentie die haalbaar is voor de PWM-pulsen.Omdat deze beperkt zal worden door de minimale pulsbreedte voor PWM1 en PWM2 dienodig is voor de gebruikte levelshifter, wordt dit besproken in Hoofdstuk 7 Snelheidsregeling .

Hoofdstuk 4. Generatie van PWM-pulsen 31

(a) PWM-pulsen: periode (b) PWM-pulsen: dode tijd

Figuur 4.10: Generatie van PWM-pulsen: simulatieresultaat

Hoofdstuk 5

Aansturing van de uitgangstrap

met behulp van een levelshifter

5.1 Inleiding

Het (laagspanning-) sturingscircuit kan een uitgangstrap bestaande uit hoogspanningscom-ponenten niet rechtstreeks aansturen. Er zijn een aantal extra circuits nodig die de sturendesignalen omvormen om zo de hoogspanningscomponenten te kunnen aansturen. Men spreektvan drivers of levelshifters. De noodzaak hiervan is schematisch voorgesteld in figuur 5.1.

Figuur 5.1: Noodzaak van de levelshifter voor de aansturing van de bovenste IGBT in de uitgangs-trap

32

Hoofdstuk 5. Aansturing van de uitgangstrap met behulp van een levelshifter 33

Voor het aansturen van de onderste IGBT is er op het eerste zicht geen probleem. Het digitaalopgewekte PWM-signaal kan inderdaad rechtstreeks de gate van deze IGBT sturen, uiteraardmits toevoegen van een buffer.

Het aansturen van de bovenste IGBT brengt wat meer problemen met zich mee. Eerst envooral is het duidelijk dat het zonder meer aanleggen van een stuursignaal dat gedefinieerdis tussen 3, 3 V en de massa voor problemen zal zorgen. Het signaal moet verschoven wordennaar de juiste spanningen. Bovendien zijn beide IGBT’s in de tak van het n-type. Om decomponent aan te schakelen is dus een spanning op de gate nodig die 3, 3 V hoger is dan zijnkathodespanning. Het is evident dat in aan-toestand gewenst is dat de spanningsval overde IGBT zo laag mogelijk is. Bijgevolg zal de kathodespanning niet veel lager zijn dan devoedingsspanning en is dus aan de gate een spanning nodig hoger dan deze voedingsspanning.Dit vergt het extra circuit waarover dit hoofdstuk handelt.

In dit hoofdstuk wordt de levelshifter besproken die zal dienen voor het aansturen van eentak van de H-brug. Door twee van deze takken te gebruiken vormt men uiteraard een H-brug(zie 2.1 H-brug).

5.2 Principeschema

In de literatuur zijn heel wat verschillende types van levelshifters te vinden. Voor het ontwerpvan het circuit is vertrokken van een Cascode-driven Bootstrapped levelshifter [6] waarvan hetschema getoond is in figuur 5.3.

5.2.1 Werking

Figuur 5.2: Karakteristiek van een transistor geschakeld als niet-lineaire weerstand

De geschikte gate-kathodespanning VGK,IGBT2 voor de bovenste IGBT wordt gegenereerddoor een stroom I te sturen doorheen een actieve last . Dit is de transistor M6 waarvan gateen drain verbonden zijn. Als gevolg wordt deze transistor bedreven in het triodegebied en isdus geschakeld als een niet-lineaire weerstand. Een gepaste stroom I zal bijgevolg aanleiding

Hoofdstuk 5. Aansturing van de uitgangstrap met behulp van een levelshifter 34

Figuur 5.3: Basisschema van de ontworpen levelshifter

geven tot de gewenste spanningsval VGK,IGBT2, in dit geval 3, 3 V. De karakteristiek van eentransistor die op zo’n manier geschakeld is, staat weergegeven op figuur 5.2.

Om de stroom I te kunnen injecteren in de actieve last, worden 2 stroomspiegels gebruikt.De laagspannings-NMOS stroomspiegel M1 − M2 zorgt voor de generatie van de stroom I ′.Een andere spiegel M4 − M5 gaat deze stroom aan de hoge kant spiegelen (en eventueelschalen) en bestaat uit hoogspanningscomponenten. Transistor M3 is essentieel en bepaalt ofde stroomspiegel M4−M5 al dan niet aangestuurd wordt. Deze transistor zorgt dus voor hetaan- of afschakelen van de IGBT bovenaan, IGBT2. Het PWM-signaal zal aan de gate vandeze transistor gelegd worden.

Deze bespreking gaat enkel maar op als de spanning Vbootstrap een waarde heeft die ver genoegboven de voedingsspanning ligt. De exacte waarde is niet zo belangrijk omdat het de stroom I

is die de gate-kathodespanning VGK,IGBT2 voor de bovenste IGBT zal vastleggen. Met behulpvan een bootstrapcapaciteit is het mogelijk om deze spanning op te wekken. Gedurende detijd dat IGBT1 geleidt, zal de capaciteit doorheen de diode opgeladen worden tot iets minderdan de voedingsspanning. Merk dus op dat een bepaalde minimale pulsduur van het signaalPWM1 vereist is. Als de bovenste IGBT dan zal geleiden, staat de uitgangsklem Vout opeen spanning dicht bij de voedingsspanning (en dus ook de onderste plaat van de capaciteit).De bovenste plaat of dus Vbootstrap zal initieel een waarde aannemen die ongeveer 2 keer devoedingsspanning bedraagt aangezien de lading aanvankelijk op de capaciteit blijft zitten.Uiteraard zal de capaciteit ontladen worden met een stroom I ′ + I en zal Vbootstrap afnemen.

Hoofdstuk 5. Aansturing van de uitgangstrap met behulp van een levelshifter 35

Door een goede dimensionering is het mogelijk om ervoor te zorgen dat Vbootstrap hoog genoegblijft gedurende de tijd dat de bovenste IGBT geleidt.

Figuur 5.4: Golfvormen horend bij het principeschema van figuur 5.3, met als last een DC-motorgeschakeld tussen Vout en VHV,2 = 12, 5 V

De golfvormen die horen bij dit principeschema zijn getoond in figuur 5.4. Volgende dimen-sionering werd hierbij gebruikt: I ′ = 21µA

I = 270µA(5.1)

C = 1, 5 nF (5.2)

De PWM periode is 100µs. Met deze stroom I werd IGBT2 in minder dan 1µs opgeladen.Om C minimaal te ontladen werd er ook voor gezorgd dat de stroomspiegel een schalinguitvoert: door M4 vloeit een stroom I ′ die te verwaarlozen is ten opzichte van de I = 270µAdoor M5 (die nodig is om de gatecapaciteit van IGBT2 snel op te laden). De dimensioneringvan de overige componenten is hier nog van geen belang.

Hoofdstuk 5. Aansturing van de uitgangstrap met behulp van een levelshifter 36

Figuur 5.5: Detail van een PWM periode uit figuur 5.4

5.2.2 Specificaties

Het ontwerp van de uitgangstrap is onderworpen aan enkele eisen. Eerst en vooral was het debedoeling om het volledige systeem monolithisch te integreren. De meeste specificaties voorde levelshifter vloeien hier dan ook uit voort en worden hieronder opgesomd.

Monolithisch geıntegreerd Het volledige systeem moet op 1 silicium chip komen. Ditbetekent dat geen externe componenten toegelaten zijn voor de levelshifter, met uit-zondering van enkele onderdelen voor de correcte instelling van het circuit. Voor debootstrapcapaciteit legt dit de belangrijkste beperking op. Capaciteiten nemen veelruimte in beslag en moeten dus zo klein mogelijk gehouden worden.

Compact Het design moet zo weinig mogelijk siliciumruimte in beslag nemen.

Stroomniveau Later tijdens het ontwerp is besloten om de stroom in de H-brug te beperkentot 0, 5 A om zo de chipoppervlakte van dit eerste prototype beperkt te houden.

Efficientie Een redelijke efficientie van het vermogensgedeelte.

Hoofdstuk 5. Aansturing van de uitgangstrap met behulp van een levelshifter 37

5.2.3 Problemen bij het principeschema

Het belangrijkste probleem dat optreedt is de beperkte grootte van de bootstrapcapaciteit.Een kleinere condensator betekent een kleiner ‘stroomreservoir’ en lage stromen leiden op hunbeurt tot het traag op- en ontladen van andere capaciteiten (onder meer de gatecapaciteitvan de IGBT’s). Dit heeft traag schakelen in de H-brug tot gevolg. Uiteraard is dit nietgewenst als de schakelverliezen beperkt moeten worden. Het principeschema hierboven biedtweinig vrijheidsgraden en zal enkel werken als de bootstrapcapaciteit voldoende groot is (de1, 5 nF capaciteit (5.2) uit het principeschema is ongeoorloofd groot om op chip te integreren).Daarom wordt dit basisschema aangepast om het hoofd te bieden aan enkele problemen.

Verder is er steeds een fundamenteel probleem bij het ontwerp van levelshifters. Stromenzijn niet heel nauwkeurig in te stellen op chip waardoor de spanning VGK,IGBT2 op figuur 5.3ook niet heel nauwkeurig gekend is bij ontwerp. Zelfs al zouden de stromen op chip perfectbepaald zijn, dan nog is het mogelijk dat VGK,IGBT2 een foutieve waarde aanneemt doorparametervariaties. De VT van de transistor in de actieve last M6 is bijvoorbeeld niet exactgekend. VGK,IGBT2 is een vrij kritieke spanning. Deze mag zeker niet meer dan 3, 6 V bedragen(om doorslag van het gate-oxide te vermijden) maar ook niet minder dan 3, 3 V want dan zijnde geleidingsverliezen in de IGBT groter. Om deze redenen wordt de regelweerstand R externaangebracht zodat VGK,IGBT2 op de gepaste waarde kan ingesteld worden.

5.3 Ontworpen schema

Het schema dat ontworpen werd voor de levelshifter is afgebeeld in figuur 5.6. Het basisprin-cipe is nog steeds aanwezig, maar er werden enkele extra circuits toegevoegd (hierna takkengenoemd) om snel schakelen mogelijk te maken. Aan de hand van figuur 5.6 kunnen volgendetakken onderscheiden worden.

Regime-tak (zie figuur 5.7) Deze tak komt in wezen overeen met het principeschema vanfiguur 5.3. In regime (“lange tijd” na aanschakelen van IGBT2) genereert deze tak eenVGK,IGBT2 van 3, 3 V. Echter de stroom die deze tak levert is te laag om de gatecapa-citeit van IGBT2 snel op te laden of te ontladen.

Ontlaad-tak(ken) (zie figuur 5.8) Dit circuit zal ervoor zorgen dat IGBT2 snel kan af-schakelen.

Laad-tak (zie figuur 5.9) Dit circuit zal ervoor zorgen dat IGBT2 snel kan aanschakelen.

Elk van deze onderdelen wordt hieronder in meer detail besproken.

Hoofdstuk 5. Aansturing van de uitgangstrap met behulp van een levelshifter 38

Figuur 5.6: Volledig schema van de levelshifter, zoals ontworpen in Cadence

5.3.1 De regime-tak

De werking van de regime-tak is volledig zoals besproken in 5.2 Principeschema. De ontwor-pen schakeling is getoond in figuur 5.7. Zoals hoger reeds aangegeven, is de functie van deze

Hoofdstuk 5. Aansturing van de uitgangstrap met behulp van een levelshifter 39

Figuur 5.7: De onderdelen van de regime-tak

tak een stroom te sturen door een actieve last met als doel de gewenste spanning VGK,IGBT2

erover op te wekken. De actieve last bestaat nu uit 3 transistoren M14 − M16 in serie omsiliciumoppervlakte uit te sparen. Een transistor geschakeld als actieve last gedraagt zichnamelijk als een niet-lineaire weerstand. Hierdoor zal een kleine stroom gestuurd worden metals doel een spanning van 3, 3 V op te wekken. Om dit mogelijk te maken zal een transistormet een uiterst kleine W

L verhouding nodig zijn, of dus een zeer lange transistor. Voor eentransistor geldt namelijk benaderend:

IDS = µCoxW

L

((VGS − VT ) VDS −

V 2DS

2

)(5.3)

De karakteristiek van de niet-lineaire weerstand (VG = VD) is dus:

IDS = µCoxW

L

(V 2

DS

2− VT VDS

)(5.4)

Uit (5.4) volgt dus dat WL zeer klein moet zijn om met een kleine stroom IDS een grote

spanning VDS over de transistor op te wekken. Met courante waarden van de technologischeconstanten geeft dit bijvoorbeeld:

Hoofdstuk 5. Aansturing van de uitgangstrap met behulp van een levelshifter 40

IDS = 5µA = 50µAV2

W

L

(3, 3 V2

2− 0, 6 V 3, 3 V

)(5.5)

W

L= 2, 9× 10−2 (5.6)

Door 3 niet-lineaire weerstanden in serie te plaatsen, zijn de afzonderlijke transistoren eenstuk kleiner. W wordt ook liefst niet minimaal (0, 5 µm) gekozen omdat de transistoren danminder nauwkeurig zijn.

Op figuur 5.7 is ook te zien dat de stroomspiegel M1 − M4 nu uitgevoerd is als een casco-deschakeling. De gunstige eigenschappen van de cascodeschakeling zijn hier niet zo zeer vanbelang. Wel is deze schakeling gekozen om R1 niet te groot en de W

L van de transistoren inde stroomspiegel niet te klein te hoeven maken. Er moeten namelijk kleine stromen opgewektworden. Hierop wordt teruggekomen bij de dimensionering.

Een ander verschil met het principeschema is dat diode D6 niet rechtstreeks met de voe-dingsspanning is verbonden, maar door middel van een spanningsdeler. Door R7 toe tevoegen zal de maximale stroom door de diode beperkt worden. Indien deze weerstand erniet zou staan, dan zou D6 veel groter moeten zijn om de grote laadstroom aan te kunnen.Het opladen van C zal nu wel trager gebeuren, namelijk met een tijdsconstante R7C. Eentweede weerstand R8 vormt een spanningsdeler samen met R7. Het is namelijk zo dat eenMetal 2-2.5 capaciteit een doorslagspanning heeft van minimaal 25V. Om hier toch wat mar-ge op te behouden zorgt de spanningsdeler dat de maximale spanning over C beperkt blijfttot 20 V.

Dimensionering van de regime-tak schakeling

De bootstrapcondensator C Metal 2-2.5 :