6 MOSFET - fhirose.yz.yamagata-u.ac.jpfhirose.yz.yamagata-u.ac.jp/img/mos9.pdf · 図2 mosfet...

Transcript of 6 MOSFET - fhirose.yz.yamagata-u.ac.jpfhirose.yz.yamagata-u.ac.jp/img/mos9.pdf · 図2 mosfet...

Internet 版 2015/7/22 版

73

第 6 章 MOSFET

能動動作をする半導体デバイスとして、東の横綱をバイポーラトランジスタとするなら、

MOSFET はさながら西の横綱といったところであろう。MOSFET は理解する過程でキャ

リアの拡散の概念を必要とせず、オームの法則と電磁気学の基礎があれば理解できる。前

章を読み進めた読者にとっては大変簡単に思われるかもしれない。この章でほぼ集積回路

に登場するすべてのデバイスを理解することになるため、一気に読んで自分のものにして

いただきたい。これを理解すれば、半導体デバイスのほとんどをカバーできることであろ

う。

1. MOSFET の概略

MOSFETはMetal-oxide-semiconductor

Field Effect Transistor、金属-酸化物-半導

体接合電界効果トランジスタの略称である。

図 1 に示されるように、p 型の Si 基板にn

型の領域を 2 か所作り、その 2 か所を橋渡

しするように MOS キャパシタを作りつけ

たものである。それぞれの領域に金属電極

を形成して、ソース、ドレイン、そしてゲ

ートとする。図 1 の例はnチャネル型

MOSFET の例であるが、nとpを入れ替え

るとpチャネル型となる。

図 1 nチャネル型 MOSFET の模式図

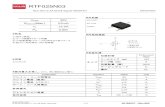

図2に MOSFET の回路記号を示す。N

チャネル MOS では矢印がゲートに向かう

形で記されるが、バイポーラトランジスタ

の npn 型トランジスタとは逆になるので初

学者は気をつけてほしい。

nチャネル MOS pチャネル MOS

図2 MOSFET の回路記号

MOSFET の電流の流れを理解するため

に、図3の回路図を見てほしい。ここで示

される例は n チャネル型の例である。ソー

ス(S)に対してドレイン(D)の電位を高

くして、ソースゲート間に電圧(Vgs)を加

えると、ドレインに電流が流れる。つまり

ゲートに電位をかけることで、ドレイン電

流を自由に変化させることができる。この

とき、ゲートへの電流の流れこみは極めて

微小であり、ソースゲート間の内部インピ

ーダンスは無限大としてよい。実際には

MOSFET の規模( 大ドレイン電流)にも

よるが1MΩ以上と考えてよい。つまり

MOSFET は極めて高い出力インピーダン

p型半導体基板

n型 n型

SiO2

ソース

ゲート

ドレイン

ソース(S)

ドレイン (D)ゲート

(G)

ソース(S)

ドレイン (D)ゲート

(G)

電極

電極

電極

MOS キャパシタ

Internet 版 2015/7/22 版

74

スをもつ回路からの直接駆動が容易である。

したがって、ゲート駆動にバッファーアン

プが不要であり、回路が簡素化できるとい

うバイポーラにはない好ましい特徴がある。

(ただし、パワー用 MOSFET では例外で

ある。入力の容量がおおきいため、バッフ

ァーアンプは必要になる。)

この電圧電流増幅動作において、Vgs と

ドレイン電流 Idの関係を比例するとして近

似したときに、比例係数 gmが相互コンダク

タンスと呼ばれる。

I =g V 1

この数値はバイポーラトランジスタでは電

流増幅率βに相当するもので、MOSFET を

用いた電圧増幅回路を設計する上で大変重

要な特性値となる。

図3に MOSFET の小信号時に等価回路

を示す。ゲートソース間は無限大のインピ

ーダンスであるため、回路上のソースとド

レイン間は接続されていない。ドレインソ

ース間にはg V で表される定電流素子と

内部抵抗 rd の並列で記述される。交流特性

の計算のために、G-S 間、G-D 間の付帯容

量をいれてあるが、低周波数でこの容量の

存在が無視できるときは、はずして計算を

してもさしつかえない。この等価回路は略

式のものであるが、回路の利得特性、周波

数特性計算には十分に耐えるものである。

FETを用いた電子回路の計算方法は他書

にゆずりたいが、図4に示されるソース接

地型の電圧増幅器の利得は

Av = Vout/Vin = -gmRd (1)

で表されることを覚えておきたい。

図3 MOSFET の略式等価回路

図4 ソース接地型増幅回路の例

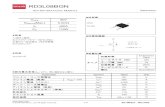

図4に MOSFET の代表的な Id-VDS特性

を示す。バイポーラとほぼ同様の飽和特性

が見られるが、ドレイン電流は Vgsに依存

して増加していくのが特徴である。ソース

ドレイン間の電圧がゲート電圧より大きく

なると、より正確には Vgs-VT(閾値電圧)

より大きいところでは、ドレイン電流が飽

和し、飽和領域と呼ばれる。この領域では

MOSFET の D-S 間はあたかも定電流素子

として動作する。また飽和領域では、ドレ

イン電流はゲート電圧の2乗に比例すると

考えてよい。ソースドレイン間の電圧が Vgs

-VTより低いところでは線形領域と呼ば

れる。閾値電圧については、後節の MOS

キャパシタのところで詳しく説明する。

DD

SS

rd

gmvg

CGD

CGS

G G

D

S

G

RD

Vout

Vin

Internet 版 2015/7/22 版

75

図5 MOSFET の Id-VDS特性

2. これで一発理解 MOSFET

MOSFET のゲート金属の直下は絶縁膜、

そして半導体の三層構造となっている。こ

の部分は MOS キャパシタと呼ばれ、絶縁膜

が誘電体層として働く平行平板コンデンサ

をみなせる。図2に示される MOS キャパ

シタの金属膜に正バイアスを加えると、金

属膜側が正に帯電し、半導体の絶縁膜側が

負に帯電する。コンデンサとみなせば、非

常にシンプルに理解できる。

図 6 nチャネル MOS とコンデンサ

負に帯電するということは p 型半導体で

電子が集まるということである。実際には、

電子がソースから流入し電子が集まる。電

子が集まった所は、電子の密度がホールよ

り多くなりn型化する。p 型半導体でも

MOS 界面はn型化すると考える。界面のn

型化した部分は電流の通り道となり、n型

チャネルという。”channel”は小道の意味で

ある。

図 3 正バイアスをかけたnチャネル MOS

ここまで説明したら MOSFET の通電の

仕組みの理解は容易であろう。MOSFET の

ソースとドレイン間に電池を接続し、ゲー

トに無バイアスとしたら、ソースドレイン

間は n-p-n 構造であり、2個のダイオード

が方向違いに接続されているとみなせ、ソ

ースとドレイン間は絶縁状態となる。した

がって、ドレイン電流は流れない。

図 7 ゲート無バイアス時の MOSFET

しかし、これにゲートとソース間に電池

を追加してみよう(図8)。このとき p 型の

半導体基板の底はソースに接続をしたとす

る。すると、絶縁膜下にn型チャネルがで

き、ソースとドレイン間は n-n-n で結ばれ、

電流が流れる。このとき、ドレイン電流は

ゲートソース間のチャネル抵抗で電流が決

まる。ゲートにかかる正バイアスが大きく

0 5 10.0 Vds0

10mA

20mA

Id Vgs=4V

3V

2V

1V

線

形

領

域

飽和領域

Vgs-VT

絶

縁

膜

金

属

膜

p型半導体

絶

縁

膜

p型半導体

コンデンサなのだ

eeeee

n型チャネル

G S D

np

n

S D

S―D 間は絶縁状態

Internet 版 2015/7/22 版

76

なれば、それに応じて、コンデンサの Q=

CV の式からもわかるように、チャネルのな

かの電荷が増えて、チャネル抵抗が下がり、

ドレイン電流が増加する。ここで断わって

おくが、チャネル間は完全に抵抗と等価で

はない。MOSFET のソースドレイン間の電

圧電流特性からわかるように、飽和領域と

線形領域があり、飽和領域ではチャネルは

定電流素子として機能する。このメカニズ

ムの理解には後節で説明するピンチオフの

説明が必要である。

図 8 ゲートバイアス時の MOSFET

線形領域と飽和領域のドレイン電流の式

を説明する。これも詳細な説明は後節で行

うが、非常に単純な理解を試みる。

線形領域

I μC V V V V (3)

飽和領域

I μC V V (4)

この式において、W はチャネルの幅、L

はチャネルの長さ、μは半導体中の電子の

移動度、Cox は MOS キャパシタの単位面

積当たりの容量である。VTとは閾値電圧と

よばれ、チャネルに電子が現れるのに必要

なゲート電圧であるが、詳しは後節の MOS

キャパシタで説明する。線形領域の例を取

って説明すると、図 6 に示される、直方体

のチャネルに MOS キャパシタ―の半導体

側の電荷が詰められていると考えることが

できる。

図 9 線形領域のチャネルの模式図

チャネル内の電荷の総量は Q=CV の式より、

Cox と VGの積になるような気もするが、ゲ

ート電圧に対して、閾値電圧 VT分だけ目減

りするのと、ドレイン付近では VDの電位が

かかってその分も目減りする。VDの目減り

分はチャネル内でもソースに近くなるほど

影響はなくなるので、平均として 1/2VD だ

け目減りすると考える。つまり、チャネル

内には Cox(VG-VT-1/2VD)分の面密度だ

け電子がいると考える。チャネル電流を出

すには、電荷の面密度×電界×チャネル幅

×移動度であるので、(3)式が導出される。

I C V V ― V W μ

面電荷密度 電界 幅 移動度

このように、ドレイン電流は電荷密度、移

動度、電界強度の積で表される、つまりオ

G S D

n p

n

n型チャネルは 電流小路

電流が流れる

e eee e

e e e

E=VD/L

W

L

Cox(VG-VT-1/2VD)

分の面密度で電

子がいると考え

n

ソ

|

ス

ド

レ

イ

ン

Internet 版 2015/7/22 版

77

ームの法則をもとに理解ができる。

飽和領域の式については、チャネルのド

レイン付近にピンチオフの部分ができ、チ

ャネルのドレイン端はゲート電圧と同じに

なっていると考え、線形領域の式の VD を

VG-VTで置き換えると、飽和領域の式が導

かれる。

3. MOSFET

MOSFET の動作機構を理解するために

は一歩戻って、ゲートの部分の MOS キャパ

シタの理解が必要である。

MOS キャパシタは図6に示されるよう

な金属と酸化膜(絶縁膜)と半導体の3層

構造からなるコンデンサーである。図 10 の

ように p 型の半導体で作られた場合、n チ

ャネル型 MOS とも呼ばれる。

図 10 n チャネル型 MOS

以降、金属に正バイアスがかけられた場

合、負バイアスがかけられた場合でキャリ

アがどのように蓄積されるかについて説明

する。

(1) 正バイアス VM>0 の場合

この場合、金属側に正電位がかかり、金

属が正に帯電する。そこから半導体にむけ

て電気力線が発せられ、p 型半導体の絶縁

膜との界面付近のホールがより遠ざかるよ

うに押しのけられ、その部分に負の固定電

荷が現れ、空乏層となる。また VMがある

程度大きくなるとp型半導体の表面付近に

電子が誘起される。このとき、電子が現れ

た部分を反転層と呼ぶ。

以上説明した動作をバンド図を用いて

説明する。図11に反転層が形成されてい

るときの MOS キャパシターのバンド図を

示す。

図 11 空乏層が形成されている MOS キャパシタ

のバンド図

金属層に正電位が加わると、半導体側の界

面部分が空乏化しバンドに曲がりが生じる。

空乏層幅を xpとすると、バンドが曲がって

生じる空乏層電位φS は次の式であらわさ

れる。この式は、 V のポアソン式か

ら導かれる。

φ ∬ dx x (5)

正バイアスが大きくなり、真性時のフェ

ルミレベルを Ei とすると Ei-Ef<φSにな

ると、表面でのフェルミレベルがバンド中

央より上に位置することになる。このとき

表面はn型となり、電子が蓄積され反転層

が形成される。

p型半導体 VM 絶

縁

膜

金

属

EF

EF

EV

EC

金属層

VM φS

空乏層 半導体層

xp

EiEi-EF

Internet 版 2015/7/22 版

78

図 12 反転層の形成されている MOS キャパシ

タのバンド図

蓄積層が形成される条件は、経験上、

2(Ei-Ef)=φS (6)

であることが知られている。半導体層のフ

ェルミレベルとフェルミ中央との差(Ei-

Ef)は、p型半導体であれば、ドーピング濃

度を NAとして、ドーピング十分に活性化さ

れているとされたときに、

E E log (7)

で表され、n型半導体であれば

E E log (8)

であらわされる。これらの式は、第2章で

説明されるボルツマン関数から容易に求め

られる。

このように反転層が形成されると、バン

ドの曲がりが生じているところの空乏層の

幅は金属膜にかけられた電位に依らずほぼ

一定になる。蓄積層形成時の空乏層の幅 xinv

は、(5)と(6)式から導出することができる。

x E E (9)

ここで、反転層ができたときの、半導体表

面に誘起される電荷の総量 QSを求める。

QSは、MOSFET のドレイン電流を計算す

るために重要な数値である。ここで覚えて

おきたいこととして、表面電荷 Qs は空乏

層内の固定電荷量 Qd と蓄積層の電子の電

荷量 Qinv の和になる。

Q Q Q (10)

空乏層の固定電荷量 Qd は

Q qN x

= 4ε ε qN E E (11)

となる。

Qinv は、外部印加電圧で決まる。つまり

MOS キャパシタの容量 C は、絶縁膜の容

量 Cox と空乏層容量 Cinv の直列接続にし

た合成容量となるが、コンデンサの蓄積電

荷の計算式から

Q CV V (12)

となる。絶縁膜の容量 Cox と空乏層容量

Cinv はそれぞれ、次の式で表される。

C =ε ε /x

(13)

C =ε ε /x (14)

この式において、ε 、xoxはそれぞれ絶縁膜

の比誘電率、膜厚である。

(2) 負バイアス VM<0 の場合

この場合は、p 型半導体のホールが絶縁

膜側に引き寄せられ、多数キャリアが蓄積

されるために、蓄積領域と呼ばれる。この

ときの表面に誘起される電荷総量 Qs は

Q C V (15)

で表される。

EF

EFEV

EC

金属層

VM

半導体層 蓄積層

EFが Eiより高くなり

n型化する。

Internet 版 2015/7/22 版

79

4. MOS キャパシタの C-V 特性

MOSFET の試作評価において、ゲート金

属と半導体間の電圧-容量特性(C-V 特性)

を取得することが一般的になされる。この

特性を取得することで、閾値電圧、界面電

荷密度、相互コンダクタンスの見積もりが

可能になる。ここでは、MOS キャパシタの

C-V 特性について解説する。

図 13に典型的なnチャネル MOSの C-V

特性を示す。金属の電圧が負である場合は

蓄積領域となり、MOS キャパシタは絶縁膜

の容量 Cox と等しくなる。一方、正バイア

スの領域になると、半導体層に空乏層が形

成され、容量は低下してくる。実際の容量

測定では、DC バイアスを重ねた高周波電

圧をMOSにかけて、高周波電流を測定し、

容量を計算するが、高周波数を使うか低周

波数を使うかで、正バイアスの容量特性は

変わってくる。例えば典型的な SiMOS キ

ャパシタでは、1kHz 以上の高周波では蓄積

領域での電子の生成消滅が高周波信号に応

答できず、この場合蓄積電荷は測定上みえ

てこなくなる。この場合、MOS キャパシタ

の全体容量は Cox と Cinv の直列成分とな

る。10Hz 以下の低周波で測定する場合は蓄

積電荷の生成消滅が十分応答できるように

なり、MOS キャパシタの全体容量は Cox

となる。低周波数測定で正バイアス領域で

容量が増加し始めるバイアス点は、反転領

域ができはじめの閾値電圧 VTとなる。閾値

電圧は MOSFET におけるドレイン電流が

流れだすゲートバイアス点を表し、

MOSFET のデバイスとの性能を評価する

上で大変重要な数値である。

C-V 特性を周波数を変えながら測定する

と、ある程度の高周波になると蓄積領域の

容量が減少してくる。この境目の周波数は

半導体層のキャリアの生成、消滅の速度に

関係しており、境目の周波数からキャリア

の生成、消滅のライフタイムを見積もるこ

とが可能である。

図 13 n チャネル MOS の C-V 特性例

C-V 特性の理論式は次のようにあらわ

される。この式は負バイアスから閾値電圧

までの範囲で有効である。

=1 V 1 (16)

5. 閾値電圧(しきいちでんあつ)

閾値電圧は MOSFET としてドレイン電

流を流すために必要なゲート電圧を意味し、

これを計算することはデバイス設計におい

て重要である。閾値電圧は MOS キャパシ

タにおいては、金属膜に電位をかけて、半

導体層に反転層ができるときの金属膜の電

位のことである。このときに、半導体での

バンドの曲がりである空乏層電位φSが、

2(Ei-Ef)に等しくなる。このときの空乏

層内の固定電荷量 Qd が、

Q qN x

= 4ε ε qN E E (17)

C

VM 0

低周波数測定(10Hz 以下)

高周波数測定

閾値電圧 VT

Internet 版 2015/7/22 版

80

で表され、この Qd が MOS キャパシタの両

端に誘起される。閾値電圧で正バイアスを

かけたとの MOS キャパシタは絶縁膜の容

量 Cox と空乏層容量の Cinv の直列で表さ

れる。

Cox Cinv

その両端の電圧は

V 4ε ε qN E ECox CinvCoxCinv

(18)

空乏層内の固定電荷を Cox と Cinv の直列

容量で割り算した値になる。

以上求めた閾値電圧は実際の金属の仕事

関数φMと半導体の仕事関数φSiが等しい

とした式である。異なる場合は、

φMS=φM -φSi (19)

としたときに、この分を VTに加える必要が

ある。この時の閾値電圧は、

V φ +

4ε ε qN E ECox CinvCoxCinv

φ +2 E ECox

(20)

となる。参考までに、p型 Si の仕事関数は

φ 4.6 log (21)

で表される。また金属の仕事関数であるが、

代表的な金属の仕事関数を記載しておく。

表 2 おもな金属材料と仕事関数

材料 仕事関数 (eV)

Al 3.2

Au 4.0

Ti 4.1

W 4.5

閾値電圧はこのほか、絶縁膜中に含まれ

る電荷や、界面でのトラップ準位に固定さ

れた電荷の影響を受ける。酸化膜中の電荷

は正の固定電荷であり、半導体界面に負の

電荷を誘起する。また、界面の電荷は電子

が捕獲された場合、負の固定となる。この

場合、界面電荷を Qsとすると、閾値電圧は

Qs/ Cox分だけ減じられることになる。界面

電荷影響を含めた閾値電圧の式は次のよう

になる。

V φ +

2 E ECox

(23)

6. フラットバンド電圧

前節から述べてきたように実際の MOS

キャパシタは金属と半導体の仕事関数差や

界面電荷の影響で、バイアスをかけていな

くてもバンドに曲がりが生じている。図 14

に p 型半導体の仕事関数より小さい仕事関

数を持った金属膜をもったnチャネル

MOS キャパシタのバンド図を示す。半導体

のフェルミレベルと金属の仕事関数が一致

するように、整合する。

+ + + +

+ + + +

― ―

― ―

― ―

― ―

+Qd ―Qd

Internet 版 2015/7/22 版

81

図 14 仕事関数が低い金属をつけたときの

n チャネル MOS のバンド図

図 15 金属膜に負バイアスをかけてフラットバン

ド状態になった時のバンド図

このキャパシタにおいて、金属膜に負バイ

アスをかけると内蔵電界を打ち消して、半

導体層のバンドがフラットになる。このと

きの金属膜に印加している電圧がフラット

バンド電圧 VFBという。フラットバンド電

圧は先の(23)式の前2項までの部分である。

V φ (24)

フラットバンド電圧は C-V 特性において

は、Cox と同じ容量になるバイアス点であ

る。図 16 に示されるように、C-V 特性から

簡単によみとることができる。φMSは簡単

に計算で出せることから、フラットバンド

電圧を実測できれば、界面電荷密度を推定

することができる。すなわち、MOS キャパ

シタの性能評価にフラットバンド電圧の評

価がしばしば行われている。界面準位密度

1cm2当たり 1012/cm2が高品質にできてい

るかどうかの目安となる。

Cox

図16 C-V特性からのフラットバンド電圧の読

み取り例

7. MOSFET のドレイン電流の導出

MOSFET の断面図が図 17 に描かれてい

る。まずは簡単のために Vg>Vd の場合に

ついて考えよう。ゲートの下にはn型チャ

ネルが形成されているが、ソースに近い方

ではチャネルが太く、ドレインに近い方で

は電位が高いため、細くなっている。ゲー

ト直下の電荷面密度はドレインに近づくに

従って小さくなる傾向にある。ゲート直下

の電位はソース近傍では 0V、ドレイン近傍

では Vd になっているので、ゲート全体と

してみれば 1/2Vdとみなせる。すなわち、

絶縁膜かかる平均電圧はVG-1/2Vdとなる。

ゲート直下の平均面電荷密度 Qch は

Q C V V 1/2Vd (24)

となる。ここで閾値電圧 VT分だけゲート電

圧から引かれているのは、実質電気伝導に

寄与するのは反転層にたまる自由電子のみ

EFEV

EC

金属層

半導体層

h h h h h h

内蔵電界

EF

EV

EC金属層 半導体層

h h h h h h

負バイアス

C

VM 0

高周波数測定 VFB

Internet 版 2015/7/22 版

82

であるため、閾値電圧以上の分が反転層の

自由電子の寄与となる。

図 17 ドレイン電流計算のためのnチャネル

MOS の模式図 ―線形領域―

ソースドレイン間の電界はチャネル長 L

とすれば Vd/L である。電流密度は電荷密度、

電界、移動度の積で表されることから、チ

ャネル内の電子の移動度をμ、チャネル幅

W とすれば、ドレイン電流は次式で表され

る。

線形領域のドレイン電流の式

I μC V V V V (25)

Vg<Vd の領域になると、ドレイン付近

に空乏層が発生し、チャネルのドレイン端

のところに空乏層ができる。この空乏層は

ドレイン電圧が大きくなると広がり、ドレ

イン電流を抑える働きがあり、ドレイン電

圧が下がると狭くなり、ドレイン電流が大

きくなる。つまりこの領域ではドレイン電

流は定電流となり、その値は VD=VG-VTの

ときの電流値となる。

図 18 ドレイン電流計算のためのnチャネル

MOS の模式図 ―飽和領域―

飽和領域のドレイン電流の式は、(25)式

の VD=VG -VTで置換した形になる。

飽和領域のドレイン電流の式

I μC V V (26)

なお、MOSFET の ON 抵抗は線形領域

の式の電圧微分から求められる。ON 抵抗

は図 19 に示されるように線形領域の慨そ

うから求められる。

MOSFET の ON 抵抗の式

R = (27)

図 19 MOSFET の ON 抵抗抽出

0V VD

VG

n

p n

n型チャネル

S D 0V VD

VG

n p n

n型チャネル

S D 空乏層

0 5 10.0 Vds 0

10mA

20mA

Id Vgs=4V

3V

2V

1V

線

形

領

域

1/RON

Internet 版 2015/7/22 版

83

8. MOSFET の特性抽出法

MOSFET の評価として、移動度(電界効

果移動度)と閾値電圧が評価されている。

図 5 のようなドレイン電流とドレイン電圧

の関係を得たらならば、飽和領域において、

ドレイン電圧を固定して I ―VG の関係を

プロットすると直線関係になる。これは

(26)式から

I μC V V (27)

が得られる。直線関係の傾きから移動度が

求められ、X軸の切片が閾値電圧VTとなる。

図 19 MOSFET の Id―VG特性の例

9. 電界効果移動度

MOSFET のドレイン電流を支配する要

因にソースとドレイン間のキャリア移動度

がある。とくに、飽和領域におけるチャネ

ル移動度を電界効果移動度μeff と呼び、次

の式で表される。

μ∂Id∂Vg

∙L

WC∙

1

V V

g ∙L

WC∙

1

V V

= ∙ (28)

これに対して、線形領域でのソースドレイ

ン間のキャリア移動度を実効移動度μe と

呼ぶ。

μ ∙ ∙ g ∙ ∙ (28)

ここで得られる電界効果移動度と実効移

動度を比べると実効移動度の方がわずかに

大きい。また、これら両移動度は、結晶内

部を走行するときの移動度(バルク移動度)

に対して、1/3 から 1/4 になると理解し

ておこう。通常nチャネルの SiMOS であ

れば、電界効果移動度は 100~200cm2/Vs

程度である。ちなみにバルク移動度はドー

ピング濃度にもよるが 500~1000cm2/Vs の

範囲である。FET のチャネルでの移動度が

バルク移動度に比べて低いのは、MOS 界面

の凹凸による散乱や、トラップ準位、固定

電荷でのクーロン散乱の影響を受けるため

である。

10. MOSFET の高速動作限界と付帯

容量

MOSFET の高速動作限界を考える上で

は考慮すべきことは、チャネルを走行する

キャリアの走行時間である。これが

MOSFET の高速動作における時定数とな

る。MOSFET が線形領域にあるときは、チ

ャネル走行時間τeは、

τ (29)

で与えられ、カットオフ周波数 fc は

f = (30)

で与えられる。

飽和領域の場合のチャネル走行時間τeff

は、

VG

I

W2L

μC

傾きは

X軸との交点は

VTを表す

Internet 版 2015/7/22 版

84

τg

(31)

で与えられ、カットオフ周波数は式(30)で

計算される。チャネル走行時間は、チャネ

ル距離 L をできるだけ短くすること、かつ

ドレインソース間電圧を高くすることで縮

小できる。MOSFET 回路の動作周波数の高

速化限界は回路の電源電圧に依存するとい

われるが、これは MOSFET のドレインに

できるだけ高い電圧をかけた回路とするこ

とで、チャネル走行時間を抑制することが

できるからである。

以上計算したのは理論的な高速化限界で

あるが、実際でのリミットは、MOSFET の

付帯容量からくる。図3の等価回路に示さ

れるように、MOSFET にはゲート絶縁膜が

あり、これがゲートソース間、ゲートドレ

イン間に寄生容量となり、周辺の抵抗成分

とあわせて、時定数となる。とくにゲート

ドレイン間の寄生容量はミラー効果により、

実際の寄生容量が電圧増幅率倍となって回

路の時定数となって作用するので注意が必

要である。MOSFET は、集積回路をつくる

上でバイポーラに比べて簡素なプロセスで

形成されるため、製造コストや集積度の観

点から広く使われているが、上記要因から

バイポーラと比べて、高速動作の点では劣

る。コストか、スピードかでバイポーラと

MOS が使い分けられているのが現状であ

る。

11. 短チャンネル効果

前節でソースドレイン間のチャネル長を

小さくすることで、チャネル走行時間を抑

制し、高速化が可能であることを述べた。

しかし、チャネル長がサブミクロン以下に

なってくると、①チャネル中のドリフト速

度が飽和するため、ドレイン電圧を上げて

も、走行時間が改善されなくなる、②ソー

スおよびドレイン近傍に形成される空乏層

の影響で、閾値電圧が変動してしまう、③

ホットエレクトロンと呼ばれるチャネル間

で加速された高速電子がドレイン近傍で欠

陥を誘起し、特性が劣化してしまう、など

の問題があげられる。

特に、②の空乏層の影響であるが、ドレ

インおよびソース付近では pn 接合で空乏

層ができており、空乏層の厚みはバイアス

状態にもよるが、サブミクロンに達する(図

20)。チャネルがすっぽりと空乏層に飲み込

まれると、空乏層内の固定電荷により、閾

値電圧 Vt が低くなる方向にシフトする。つ

まり低いゲート電圧でもオンしやすくなる。

この問題は大変深刻で、わずかなマスク合

わせのずれでも、閾値電圧 Vt がずれること

になり、ソースドレイン間のオフ時の漏れ

電流や、CMOS の閾値電圧の変動につなが

る。これを回避するには、ソースとドレイ

ンのドーピング層の厚みを 10nm 程度に抑

えることが有効である。

図 20 短チャンネルでの空乏層の影響

12. 低 ON 抵抗化と DMOSFET

MOSFET は CMOS などの IC の能動素

子だけではなく、スイッチング用のパワー

ゲート

空乏層

ソース ドレイン

空乏層

Internet 版 2015/7/22 版

85

トランジスタとしても広く利用されている。

特にパワーMOS トランジスタにおいては、

バイポーラのような少数キャリアの蓄積が

ないため、極めて高速なスイッチ特性を実

現できる。このようなパワーMOS とも呼ば

れる大電力用 FET では 、ドレインを基板

の下面に形成し、縦方向に電流を流す方式

がとられる。このような縦型 MOS のアイ

デ ア は い く つ か あ る が 、 2 重 拡 散

MOSFET(Double diffusion MOSFET,

DMOSFET)が、製造工程が少なく、コスト

を抑えられることから広く生産されている。

この構造は、ゲート酸化膜をマスクにして、

pとnの拡散条件を変えて、図 21 のような

2重拡散構造を作り、表面にチャネルを形

成して、基板下面に電流を流す構造となっ

ている。

図 21 DMOSFET の構造

縦型の電流経路を持つ MOSFET は、こ

のほかトレンチ型や V 溝型などが考案され

ているが、パワーMOS 業界はデバイスの先

進性よりコストが重視されるため、製造コ

ストで有利な DMOSFET の主役は当面続

きそうである。

13. 薄膜トランジスタ(TFT)

ガラスなどのSiウェハ以外の材料基板に

薄く半導体薄膜を積層し、その薄膜を加工

してできるトランジスタを、薄膜トランジ

スタ(Thin Film Transistor, TFT)という。

薄膜トランジスタは、液晶ディスプレイの

主役となる技術であり、画素となる素子を

駆動するトランジスタとして利用される。

これはアクティブマトリクスディスプレイ

(図 22)と呼ばれるもので、各画素素子に

トランジスタを近接させることで、配線の

電流を抑制し、より高速な発色応答が可能

になる。近年、ハイビジョンなどの高精細

ディスプレイなどのニーズが高まり、より

ちらつきの少ない高品質ディスプレイの技

術開発が求められ、薄膜トランジスタにお

いてもより高い電流密度、すなわちより高

い電界効果移動度がもとめられるようにな

った。

図 22 アクティブマトリクスディスプレイの回路

構成

ゲート絶縁膜

ゲート ソース ソース

ドレイン

n

p p n+ n+

ガラス基板

n 型 n 型 p型

ソース ドレイン ゲート

データドライバー

アドレスドライバー

画素素子

図 23 薄膜トランジスタの構造

Internet 版 2015/7/22 版

86

薄膜トランジスタの構造を図 23 に示す。

薄膜トランジスタはもともと、スコットラ

ンドの Spear、LeComber らによって、グ

ロー放電によって形成さえたアモルファス

シリコン(aSi)がドーピングによって、導電

型を制御できることが報告され、それが端

緒となりアクティブマトリクスディスプレ

イへの応用がすすめられた。1980 年初頭に

aSi を用いた液晶ディスプレイが開発され

ている。しかし、aSi による薄膜トランジ

スタの電界効果移動度は 0.1cm2/Vs と極め

て低く、薄膜トランジスタのドレイン電流

が小さいことから、aSi の液晶ディスプレ

イの画面応答は極めて遅い問題があった。

その遅さは液晶の味わいとして一部ユーザ

ーには受け入れられていたものの、動きの

激しいビデオ再生のニーズから薄膜トラン

ジスタの高電流密度化の研究がすすめられ

た。その後、エキシマレーザーをアモルフ

ァス Si 膜に照射し、瞬時に膜を融解させ、

再結晶化させるレーザーアニールの技術が

活用され、ここから半導体のチャネル層で

は多結晶 Siが主流となる。これにより、電

界効果移動度が 100cm2/Vs 近くまで向上し、

液晶ディスプレイの応答性が飛躍的に改善

された。また、近年では、多結晶薄膜トラ

ンジスタをつかって、CPU を製作して、ア

クティブマトリクスディスプレイのインテ

リジェント化を試みる研究も進められてい

る。

多結晶Siによる薄膜トランジスタにおい

て内部に存在する粒界が電界効果移動度を

抑制する原因であり、粒界の影響を抑える

ために、結晶粒の巨大化が試みられている。

そのため、エキシマレーザー光の走査速度

を調整した横方向結晶化や、金属誘起結晶

化技術などの開発がすすめられている。Si

系薄膜トランジスタにおいては当面、結晶

Si なみの電界効果移動度の実現が目標とさ

れているが、粒界密度の低減と不活性化の

研究が開発課題である。

粒界のキャリア移動度へ及ぼす影響につ

いては、よくわかっていないが、粒界にお

いて、界面準位に電子が捕獲されることに

よって、ポテンシャル障壁 EBができ、バル

ク移動度μB に対して、粒界での移動度

μGB は次のアレニウスの式で表される単純

なモデルをつかって、シミュレーション等

で解析がされている。

μ μ exp (32)

図 24 粒界のバンドモデル

薄膜トランジスタの発展は多結晶Siの開

発によるところが大きいが、近年では、ZnO

などの酸化物半導体や有機半導体を利用し

た有機 FET の開発も進められている。

図 25 実験用有機トランジスタの構造

粒界障壁

界面準位に捕獲

された電子

高濃度ドープ Si

ゲート絶縁膜 有機半導体膜 ゲート電極

ソース電極 ドレイン電極

Internet 版 2015/7/22 版

87

図 25 に研究開発用で広く試作されてい

る有機 FET の構造を示す。ゲート電極と基

板をかねて高濃度の Si 基板に SiO2などの

ゲート絶縁膜を堆積し、その上に 100nm 程

度の膜厚で有機半導体膜を形成する。代表

的な有機半導体として、ペンタセンやオリ

ゴチオフェンなどの低分子材料は真空蒸着

で形成される。また P3HT などの有機ポリ

マーではクロロベンゼンなどの有機溶剤に

溶いて、ディップ法やスピンコート法で膜

として形成する。SiFET と異なるのは、ソ

ース、ドレインに異なる導電型でのドーピ

ング領域を作らないことである。有機 FET

では有機材料そのものが半絶縁性であり、

ゲートに電圧をかけて、有機材料にキャリ

アが蓄積したときに、導電性を帯び、ドレ

イン電流が流れる。ドレイン、ソースの金

属種については、できる限り有機半導体の

キャリア準位に近い仕事関数を持つものが

選定される。p型の有機半導体では Au が、

n型の半導体では Al や CaF などが用いら

れる。

有機 FET は、有機 EL ディスプレイの画

素素子の駆動用トランジスタとして利用が

期待されているが、当面はアモルファス Si

なみの電界効果移動度の実現が目標である。

多くの有機半導体がp型であり、電界効果

移動度においても、ペタンセンやポリチオ

フェン等の材料で、1cm2/Vs 近い電界効果

移動度が報告されている。n型については

C60 などのフラーレン類が使われているが、

移動度が p 型材料に比べて見劣りするのが

現状である。また有機 FET は電流密度が高

くなると、電界効果移動度が低下する傾向

にあり、大電流化においても新しいアイデ

アが必要である。

図 26 著者研究室で試作した有機 FET と特性例

有機半導体は P3HT の例

-14x10-6

-12

-10

-8

-6

-4

-2

0

Id (

A)

-80-60-40-200

Vds (V)

Vg=0 V -5 V -10 V -15 V -20 V -30 V -40 V -50 V